# Propriétés physiques des circuits

De l'architecture des portes logiques à l'impact de la nanoélectronique sur l'économie des TICs...

Yves Mathieu, Jean-Luc Danger

### Plan

#### Introduction

Inventaire des éléments nécessaires

Une source d'alimentation:

V<sub>dd</sub>

- Une source d'alimentation:

- $V_{dd}$

- Une convention logique:

$$0 = V_{ss}, 1 = V_{dd}$$

#### Inventaire des éléments nécessaires

- Une source d'alimentation:

V<sub>dd</sub>

- Une convention logique:

$$0 = V_{ss}, 1 = V_{dd}$$

Un interrupteur piloté par une tension mesurée par rapport à V<sub>ss</sub>:

- Une source d'alimentation:

V<sub>dd</sub>

- Une convention logique:

$$0 = V_{ss}, 1 = V_{dd}$$

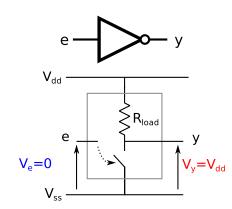

- Un interrupteur piloté par une tension mesurée par rapport à V<sub>ss</sub>:

- V<sub>e</sub> = 0 Interrupteur ouvert

- Une source d'alimentation:

V<sub>dd</sub>

- Une convention logique:

$$0 = V_{ss}, 1 = V_{dd}$$

- Un interrupteur piloté par une tension mesurée par rapport à V<sub>ss</sub>:

- V<sub>e</sub> = 0 Interrupteur ouvert

- V<sub>e</sub> = V<sub>dd</sub> Interrupteur fermé

- Une source d'alimentation:

V<sub>dd</sub>

- Une convention logique:

$$0 = V_{ss}, 1 = V_{dd}$$

- Un interrupteur piloté par une tension mesurée par rapport à V<sub>ss</sub>:

- V<sub>e</sub> = 0 Interrupteur ouvert

- V<sub>e</sub> = V<sub>dd</sub> Interrupteur fermé

- Une charge résistive: R<sub>load</sub>

- Une source d'alimentation:

V<sub>dd</sub>

- Une convention logique:

$$0 = V_{ss}, 1 = V_{dd}$$

- Un interrupteur piloté par une tension mesurée par rapport à V<sub>ss</sub>:

- V<sub>e</sub> = 0 Interrupteur ouvert

- V<sub>e</sub> = V<sub>dd</sub> Interrupteur fermé

- Une charge résistive: R<sub>load</sub>

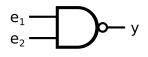

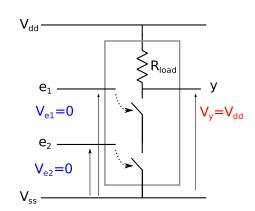

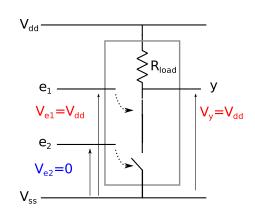

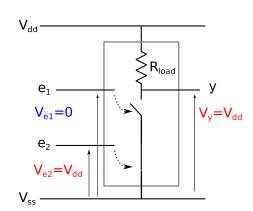

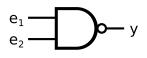

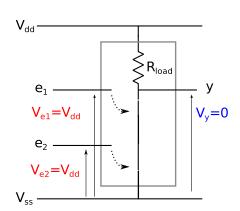

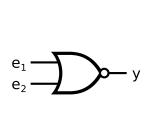

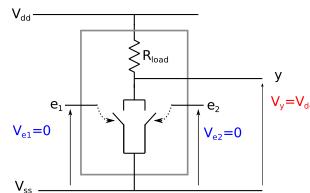

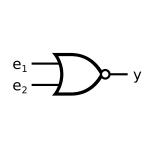

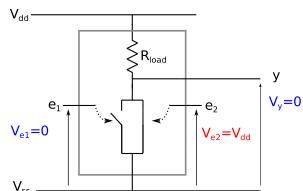

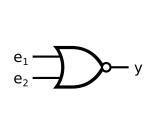

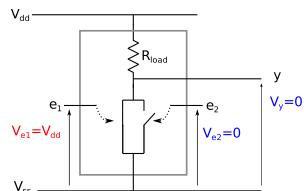

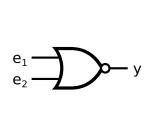

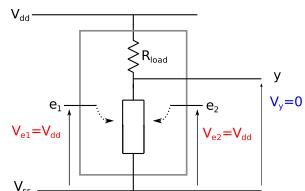

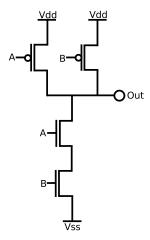

#### La porte non-et à 2 entrées

#### La porte non-et à 2 entrées

## En conclusion, c'est simple...

mais...

- Cette logique consomme en permanence lorsque la sortie de la porte logique est à 0:

- Nous aimerions réaliser des microprocesseurs qui ne consomment que lorsque l'on a besoin de réaliser un calcul...

## En conclusion, c'est simple...

mais...

- Cette logique consomme en permanence lorsque la sortie de la porte logique est à 0:

- Nous aimerions réaliser des microprocesseurs qui ne consomment que lorsque l'on a besoin de réaliser un calcul...

- Les physiciens ne savent pas réaliser d'interrupteur «idéal»(à des températures de fonctionnement raisonnables):

- Le niveau logique  $\bf 0$  n'atteint pas  $V_{ss}$ . Il n'y a pas de garantie de fonctionnement de la logique

### **Plan**

Introduction

Logique CMOS

Performances de la logique CMOS

Retour sur les lois de Moore

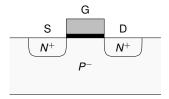

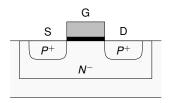

#### **Complementary Metal Oxyde Semiconductor logic**

Transistor nMOS

- Canal N

- Courant d'électrons

- Passant si  $V_{as} > V_T$

Transistor pMOS

- Canal P

- Courant de trous

- Passant si  $V_{qs} < -|V_T|$

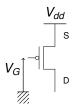

### Le transistor MOS

#### Un interrupteur électronique

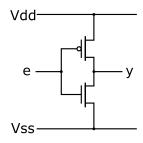

Transistor nMOS

- $V_G = V_{ss} \Leftrightarrow \text{interrupteur}$

- V<sub>G</sub> = V<sub>dd</sub> ⇔ interrupteur fermé

#### Transistor pMOS

- $V_G = V_{ss} \Leftrightarrow \text{interrupteur fermé}$

- V<sub>G</sub> = V<sub>dd</sub> ⇔ interrupteur ouvert

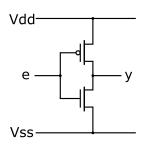

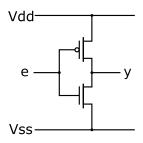

- *e* = 0

- V<sub>e</sub> = 0

- nMOS bloqué, pMOS passant

- $V_y = V_{dd}$

- y = 1

- e = 0

- V<sub>e</sub> = 0

- nMOS bloqué, pMOS passant

- $V_y = V_{dd}$

- *y* = 1

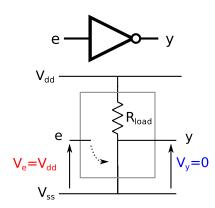

- *e* = 1

- $V_e = V_{dd}$

- nMOS passant, pMOS bloqué

- $V_y = 0$

- y = 0

- *e* = 0

- $V_e = 0$

- nMOS bloqué, pMOS passant

- $V_y = V_{dd}$

- *y* = 1

- *e* = 1

- $V_e = V_{dd}$

- nMOS passant, pMOS bloqué

- $V_{v} = 0$

- y = 0

- Consommation uniquement à l'occasion de nouveaux calculs (transitions)

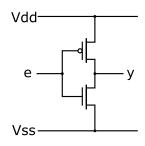

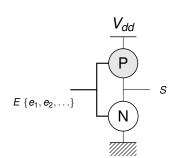

#### Généralisation à une porte complexe

Une porte avec les entrées  $\{e_1, e_2, \ldots\}$  et la sortie S.

Deux réseaux duaux:

nMOS: permet la mise à 0 pMOS: permet la mise à 1

- Les deux réseau ne doivent jamais être passants en même temps

- Pour que S soit une fonction logique:

- Si N est passant P bloqué

- Si P est passant N bloqué

La porte non-et (NAND)

exerçons nous...

■ La porte non-ou (NOR) à deux entrées.

exerçons nous...

- La porte non-ou (NOR) à deux entrées.

- La porte non-ou (NOR) à N entrées.

exerçons nous...

- La porte non-ou (NOR) à deux entrées.

- La porte non-ou (NOR) à N entrées.

- Attention, dans la pratique pas plus de 3/4 entrées (modèle trop simpliste du transistor)

exercons nous...

- La porte non-ou (NOR) à deux entrées.

- La porte non-ou (NOR) à N entrées.

- Attention, dans la pratique pas plus de 3/4 entrées (modèle trop simpliste du transistor)

- Association de portes plus simples.

exerçons nous...

- La porte non-ou (NOR) à deux entrées.

- La porte non-ou (NOR) à N entrées.

- Attention, dans la pratique pas plus de 3/4 entrées (modèle trop simpliste du transistor)

- Association de portes plus simples.

- La fonction :  $F(a, b, c) = \overline{a \cdot b + b \cdot c + c \cdot a}$

exerçons nous...

- La porte non-ou (NOR) à deux entrées.

- La porte non-ou (NOR) à N entrées.

- Attention, dans la pratique pas plus de 3/4 entrées (modèle trop simpliste du transistor)

- Association de portes plus simples.

- La fonction :  $F(a, b, c) = \overline{a \cdot b + b \cdot c + c \cdot a}$

- La porte ou-exclusif à 2 entrées.

exerçons nous...

- La porte non-ou (NOR) à deux entrées.

- La porte non-ou (NOR) à N entrées.

- Attention, dans la pratique pas plus de 3/4 entrées (modèle trop simpliste du transistor)

- Association de portes plus simples.

- La fonction :  $F(a, b, c) = \overline{a \cdot b + b \cdot c + c \cdot a}$

- La porte ou-exclusif à 2 entrées.

- Toutes les fonctions logiques ne peuvent pas se construire en une porte CMOS unique.

### **Plan**

Introduction

Logique CMOS

Performances de la logique CMOS

Retour sur les lois de Moore

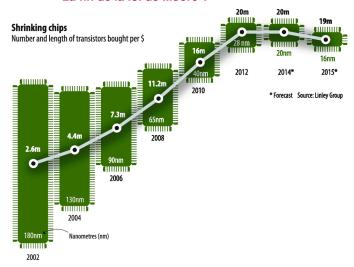

Loi(s) de Moore

- Gordon Moore, cofondateur d'Intel.

- 1966 : "La complexité des semiconducteurs double tous les ans à coûts constants"

Loi(s) de Moore

- Gordon Moore, cofondateur d'Intel.

- 1966 : "La complexité des semiconducteurs double tous les ans à coûts constants"

- Constatation devenue par la suite auto-prédictive.

Loi(s) de Moore

- Gordon Moore, cofondateur d'Intel.

- 1966 : "La complexité des semiconducteurs double tous les ans à coûts constants"

- Constatation devenue par la suite auto-prédictive.

- Ajustement des dépenses de R&D...

- Ajustement des investissements dans les usines...

#### Loi(s) de Moore

- Gordon Moore, cofondateur d'Intel.

- 1966 : "La complexité des semiconducteurs double tous les ans à coûts constants"

- Constatation devenue par la suite auto-prédictive.

- Ajustement des dépenses de R&D...

- Ajustement des investissements dans les usines...

- ... pour suivre la prédiction.

Le triomphe du "technology push"

15/30

#### Loi(s) de Moore

- Gordon Moore, cofondateur d'Intel.

- 1966 : "La complexité des semiconducteurs double tous les ans à coûts constants"

- Constatation devenue par la suite auto-prédictive.

- Ajustement des dépenses de R&D...

- Ajustement des investissements dans les usines...

- ... pour suivre la prédiction.

- Extrapolation à "La fréquence de fonctionnement des... double tous les..."

#### Loi(s) de Moore

- Gordon Moore, cofondateur d'Intel.

- 1966 : "La complexité des semiconducteurs double tous les ans à coûts constants"

- Constatation devenue par la suite auto-prédictive.

- Ajustement des dépenses de R&D...

- Ajustement des investissements dans les usines...

- ... pour suivre la prédiction.

- Extrapolation à "La fréquence de fonctionnement des... double tous les..."

- Extrapolation à "La consommation des... est divisée par deux tous les..."

#### Loi(s) de Moore

- Gordon Moore, cofondateur d'Intel.

- 1966 : "La complexité des semiconducteurs double tous les ans à coûts constants"

- Constatation devenue par la suite auto-prédictive.

- Ajustement des dépenses de R&D...

- Ajustement des investissements dans les usines...

- ... pour suivre la prédiction.

- Extrapolation à "La fréquence de fonctionnement des... double tous les..."

- Extrapolation à "La consommation des... est divisée par deux tous les..."

Le triomphe du "technology push"

ELECINF102

## Critères de performances

- La **surface**: Plus le circuit est petit, meilleur est le rendement de fabrication et donc plus faible est le coût de fabrication.

- Réduire la taille des transistors (technologue)

- Réduire le nombre de transistors (architecte)

16/30

## Critères de performances

- La surface: Plus le circuit est petit, meilleur est le rendement de fabrication et donc plus faible est le coût de fabrication.

- Réduire la taille des transistors (technologue)

- Réduire le nombre de transistors (architecte)

- La vitesse: Plus la logique est rapide, plus on peut effectuer de calculs dans la même durée de temps.

- Comment augmenter la fréquence d'horloge ?

# Critères de performances

- La surface: Plus le circuit est petit, meilleur est le rendement de fabrication et donc plus faible est le coût de fabrication.

- Réduire la taille des transistors (technologue)

- Réduire le nombre de transistors (architecte)

- La vitesse: Plus la logique est rapide, plus on peut effectuer de calculs dans la même durée de temps.

- Comment augmenter la fréquence d'horloge ?

- La consommation: Le "calcul" implique une consommation d'énergie

- Comment minimiser cette consommation ? (objets connectés...)

- Comment évacuer la chaleur dissipée ? (serveurs pour le cloud...)

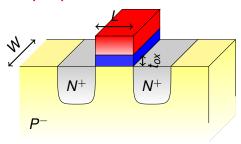

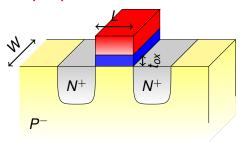

#### Le transistor MOS

Une vision plus précise

#### Le courant dans le transistor "passant"

$$I_{DS_{max}} = K_n \cdot (V_{dd} - V_{TN})^2$$

17/30

#### Le transistor MOS

Une vision plus précise

#### Le courant dans le transistor "passant"

$$I_{DS_{max}} = K_n \cdot \left( V_{dd} - V_{TN} \right)^2$$

avec  $K_n = \frac{1}{2} \mu_{0N} \cdot C_{ox}' rac{W_N}{L_N}$

#### Le transistor MOS

Une vision plus précise

#### Le courant dans le transistor "passant"

$$I_{DS_{max}} = K_n \cdot (V_{dd} - V_{TN})^2$$

avec  $K_n = \frac{1}{2} \mu_{0N} \cdot C_{ox}' \frac{W_N}{L_N}$

#### La capacité parasite de la grille du transistor

$$C_{ox} = C'_{ox} W_N \cdot L_N$$

ELECINF102

Capacité parasite

■ La sortie d'une porte en logique CMOS est reliée:

Capacité parasite

- La sortie d'une porte en logique CMOS est reliée:

- · A des fils de connection

18/30

- La sortie d'une porte en logique CMOS est reliée:

- A des fils de connection

- A des entrées de portes CMOS (grilles de transistors)

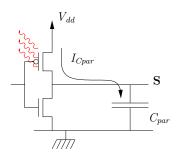

#### Capacité parasite

- La sortie d'une porte en logique CMOS est reliée:

- A des fils de connection

- A des entrées de portes CMOS (grilles de transistors)

- Ses éléments sont équivalents à une unique capacité parasite C<sub>par</sub>:

18/30

- La sortie d'une porte en logique CMOS est reliée:

- A des fils de connection

- A des entrées de portes CMOS (grilles de transistors)

- Ses éléments sont équivalents à une unique capacité parasite C<sub>par</sub>:

- qui doit être chargée dans les transitions montantes de la sortie de la porte

- La sortie d'une porte en logique CMOS est reliée:

- A des fils de connection

- A des entrées de portes CMOS (grilles de transistors)

- Ses éléments sont équivalents à une unique capacité parasite C<sub>par</sub>:

- qui doit être chargée dans les transitions montantes de la sortie de la porte

- qui doit être déchargée dans les transitions descendantes de la sortie de la porte

- La sortie d'une porte en logique CMOS est reliée:

- A des fils de connection

- A des entrées de portes CMOS (grilles de transistors)

- Ses éléments sont équivalents à une unique capacité parasite C<sub>par</sub>:

- qui doit être chargée dans les transitions montantes de la sortie de la porte

- qui doit être déchargée dans les transitions descendantes de la sortie de la porte

- Le temps de calcul d'une porte logique est directement lié à ce temps de charge et de décharge

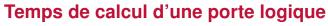

Cas d'une transition montante à l'entrée d'un inverseur

Le courant traversé par les transistors pour la charge ou la décharge de la capacités parasite C<sub>par</sub> est I<sub>DS<sub>max</sub></sub>

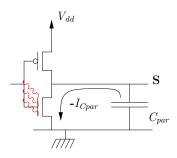

Temps de calcul d'un inverseur

Relation courant/tension dans la capacité parasite

$$I_{C_{par}} = C_{par} dV_{C_{par}} / dt$$

Temps de calcul d'un inverseur

#### Relation courant/tension dans la capacité parasite

$$I_{C_{par}} = C_{par} dV_{C_{par}}/dt$$

Courant de décharge constant identique au courant du transistor NMOS

$$I_{C_{par}} pprox I_{DSmax} = K_n \cdot (V_{dd} - V_{tn})^2$$

#### Temps de calcul d'un inverseur

#### Relation courant/tension dans la capacité parasite

$$I_{C_{par}} = C_{par} dV_{C_{par}} / dt$$

# Courant de décharge constant identique au courant du transistor NMOS

$$I_{C_{par}} pprox I_{DSmax} = K_n \cdot (V_{dd} - V_{tn})^2$$

#### Décharge de $V_{dd}$ à 0

$$t_{calc} = C_{par} rac{\Delta V}{I_{DSmax}} = C_{par} rac{V_{dd}}{K_n \cdot (V_{dd} - V_{tn})^2}$$

Temps de calcul d'un inverseur

#### Relation courant/tension dans la capacité parasite

$$I_{C_{par}} = C_{par} dV_{C_{par}} / dt$$

Courant de décharge constant identique au courant du transistor NMOS

$$I_{C_{par}} pprox I_{DSmax} = K_n \cdot (V_{dd} - V_{tn})^2$$

Décharge de  $V_{dd}$  à 0

$$t_{calc} = C_{par} rac{\Delta V}{I_{DSmax}} = C_{par} rac{V_{dd}}{K_n \cdot (V_{dd} - V_{tn})^2}$$

Augmenter la tension d'alimentation pour augmenter la vitesse (overclocking) ? (pas recommandé: voir consommation)

#### Energie dissipée et énergie stockée

Transition montante

Transition descendante

Bilan d'énergie

## Charge: Énergie fournie par l'alimentation

$$E_{Vdd} = C_{par} \int_0^{V_{dd}} V_{dd} \mathrm{d}V_s = C_{par} V_{dd}^2$$

Bilan d'énergie

## Charge: Énergie fournie par l'alimentation

$$E_{Vdd} = C_{par} \int_0^{V_{dd}} V_{dd} \mathrm{d}V_s = C_{par} V_{dd}^2$$

# Charge: Énergie potentielle stockée dans la capacité

$$E_{Cpar} = C_{par} \int_0^{V_{dd}} V_{

m s} {

m d}V_{

m s} = C_{par} rac{V_{dd}^2}{2}$$

22/30

Bilan d'énergie

## Charge: Énergie fournie par l'alimentation

$$E_{Vdd} = C_{par} \int_0^{V_{dd}} V_{dd} \mathrm{d}V_s = C_{par} V_{dd}^2$$

## Charge: Énergie potentielle stockée dans la capacité

$$E_{Cpar} = C_{par} \int_0^{V_{dd}} V_s \mathsf{d}V_s = C_{par} rac{V_{dd}^2}{2}$$

En moyenne  $C_{par} \frac{V_{od}^2}{2}$  dissipée (ou consommée) à chaque transition de la sortie de la porte

Extrapolation à un circuit intégré

Extrapolation à un circuit intégré

■ Soit *F<sub>h</sub>* la fréquence de fonctionnement du circuit

Extrapolation à un circuit intégré

- Soit *F<sub>h</sub>* la fréquence de fonctionnement du circuit

- Soit  $T_{act}$  la probabilité de transition des portes à chaque cycle d'horloge ( $T_{act} \approx 0.3$ )

#### Extrapolation à un circuit intégré

- Soit *F<sub>h</sub>* la fréquence de fonctionnement du circuit

- Soit  $T_{act}$  la probabilité de transition des portes à chaque cycle d'horloge ( $T_{act} \approx 0.3$ )

- Soit *C*<sub>total</sub> la capacité parasite totale du circuit

#### Extrapolation à un circuit intégré

- Soit *F<sub>h</sub>* la fréquence de fonctionnement du circuit

- Soit  $T_{act}$  la probabilité de transition des portes à chaque cycle d'horloge ( $T_{act} \approx 0.3$ )

- Soit *C*<sub>total</sub> la capacité parasite totale du circuit

#### Puissance consommée par le circuit:

$$P_{circuit} \approx T_{act} F_h C_{total} V_{dd}^2$$

#### Extrapolation à un circuit intégré

- Soit *F<sub>h</sub>* la fréquence de fonctionnement du circuit

- Soit  $T_{act}$  la probabilité de transition des portes à chaque cycle d'horloge ( $T_{act} \approx 0.3$ )

- Soit *C*<sub>total</sub> la capacité parasite totale du circuit

#### Puissance consommée par le circuit:

$$P_{circuit} \approx T_{act} F_h C_{total} V_{dd}^2$$

Que pensez vous de l'impact de l'overclocking sur la consommation ?

#### Plan

Introduction

Logique CMOS

Performances de la logique CMOS

Retour sur les lois de Moore

"Downsizing théorique"

- Génération technologique

- Les fondeurs visent une réduction en surface d'un facteur 2 à chaque génération.

- Génération technologique

- Les fondeurs visent une réduction en surface d'un facteur 2 à chaque génération.

- Les "fondeurs" investissent les milliards nécessaires pour cela..

- Génération technologique

- Les fondeurs visent une réduction en surface d'un facteur 2 à chaque génération.

- Les "fondeurs" investissent les milliards nécessaires pour cela..

- La longueur de grille minimale est caractéristique d'une génération technologique (90nm, 65nm, 40nm, 28nm...)

- Génération technologique

- Les fondeurs visent une réduction en surface d'un facteur 2 à chaque génération.

- Les "fondeurs" investissent les milliards nécessaires pour cela..

- La longueur de grille minimale est caractéristique d'une génération technologique (90nm, 65nm, 40nm, 28nm...)

- On utilise un facteur de réduction  $\beta = \sqrt{2}$

- Génération technologique

- Les fondeurs visent une réduction en surface d'un facteur 2 à chaque génération.

- Les "fondeurs" investissent les milliards nécessaires pour cela..

- La longueur de grille minimale est caractéristique d'une génération technologique (90nm, 65nm, 40nm, 28nm...)

- On utilise un facteur de réduction  $\beta = \sqrt{2}$

- division par  $\beta$  de la largeur W et la longueur L des transistors

- Génération technologique

- Les fondeurs visent une réduction en surface d'un facteur 2 à chaque génération.

- Les "fondeurs" investissent les milliards nécessaires pour cela..

- La longueur de grille minimale est caractéristique d'une génération technologique (90nm, 65nm, 40nm, 28nm...)

- On utilise un facteur de réduction  $\beta = \sqrt{2}$

- division par  $\beta$  de la largeur W et la longueur L des transistors

- division par  $\beta$  de l'épaisseur d'oxyde de grille  $T_{OX}$

"Downsizing théorique"

- Génération technologique

- Les fondeurs visent une réduction en surface d'un facteur 2 à chaque génération.

- Les "fondeurs" investissent les milliards nécessaires pour cela..

- La longueur de grille minimale est caractéristique d'une génération technologique (90nm, 65nm, 40nm, 28nm...)

- On utilise un facteur de réduction  $\beta = \sqrt{2}$

- division par  $\beta$  de la largeur W et la longueur L des transistors

- division par β de l'épaisseur d'oxyde de grille T<sub>OX</sub>

- division par  $\beta$  de la tension d'alimentation  $V_{dd}$  des circuits

"Downsizing théorique"

- Génération technologique

- Les fondeurs visent une réduction en surface d'un facteur 2 à chaque génération.

- Les "fondeurs" investissent les milliards nécessaires pour cela..

- La longueur de grille minimale est caractéristique d'une génération technologique (90nm, 65nm, 40nm, 28nm...)

- On utilise un facteur de réduction  $\beta = \sqrt{2}$

- division par  $\beta$  de la largeur W et la longueur L des transistors

- division par β de l'épaisseur d'oxyde de grille T<sub>OX</sub>

- division par  $\beta$  de la tension d'alimentation  $V_{dd}$  des circuits

- division par  $\beta$  de la tension de seuil  $V_T$  des transistors

Conséquences sur les performances

Conséquences sur les performances

## Évolution des capacités parasites

$$C_{ extstyle par}(eta) = (W/eta)(L/eta)(eta C_{ extstyle ox}') = rac{C_{ extstyle par}}{eta}$$

Conséquences sur les performances

## Évolution des capacités parasites

$$C_{ extsf{par}}(eta) = (W/eta)(L/eta)(eta C_{ extsf{ox}}') = rac{C_{ extsf{par}}}{eta}$$

#### Évolution de l'énergie consommée par une porte

$$E_{porte}(eta) = rac{C_{par}}{eta}(rac{V_{dd}}{eta})^2 = rac{E_{porte}}{eta^3}$$

Conséquences sur les performances

# Évolution des capacités parasites

$$C_{par}(\beta) = (W/\beta)(L/\beta)(\beta C'_{ox}) = \frac{C_{par}}{\beta}$$

## Évolution de l'énergie consommée par une porte

$$E_{porte}(eta) = rac{C_{par}}{eta}(rac{V_{dd}}{eta})^2 = rac{E_{porte}}{eta^3}$$

# Évolution du temps de calcul des fonctions combinatoires

$$t_{calc}(eta) = rac{t_{calc}}{eta}$$

Diminuer "en théorie" les coûts et la consommation

- On n'exploite pas le gain en vitesse

- $F_h(\beta) = F_h$

Diminuer "en théorie" les coûts et la consommation

- On n'exploite pas le gain en vitesse

- $F_h(\beta) = F_h$

- Le gain en surface fait diminuer les prix

- $Surf(\beta) = \frac{Surf}{\beta^2}$

Diminuer "en théorie" les coûts et la consommation

- On n'exploite pas le gain en vitesse

- $F_h(\beta) = F_h$

- Le gain en surface fait diminuer les prix

- $Surf(\beta) = \frac{Surf}{\beta^2}$

- La consommation diminue.

- $P_{circuit}(eta) = T_{act}(F_h) rac{E_{circuit}}{eta^3} = rac{P_{circuit}}{eta^3}$

Diminuer "en théorie" les coûts et la consommation

- On n'exploite pas le gain en vitesse

- $F_h(\beta) = F_h$

- Le gain en surface fait diminuer les prix

- $Surf(\beta) = \frac{Surf}{\beta^2}$

- La consommation diminue.

- $P_{circuit}(\beta) = T_{act}(F_h) \frac{E_{circuit}}{\beta^3} = \frac{P_{circuit}}{\beta^3}$

- Cette stratégie est particulièrement intéressante dans l'embarqué:

- Transition du "haut de gamme" vers le milieu, puis bas de gamme (smartphones)

- Ouverture à de nouvelles utilisations (objets connectés).

- On exploite le gain en vitesse

- $F_h(\beta) = \beta \dot{F}_h$

- On exploite le gain en vitesse

- $F_h(\beta) = \beta \dot{F}_h$

- On profite du gain en taille des transistors pour accroître la complexité du circuit

- $Surf(\beta) = Surf$

- On exploite le gain en vitesse

- $F_h(\beta) = \beta \dot{F}_h$

- On profite du gain en taille des transistors pour accroître la complexité du circuit

- $Surf(\beta) = Surf$

- La consommation ne change pas

- $P_{circuit}(\beta) = P_{circuit}$

- On exploite le gain en vitesse

- $F_h(\beta) = \beta \dot{F}_h$

- On profite du gain en taille des transistors pour accroître la complexité du circuit

- $Surf(\beta) = Surf$

- La consommation ne change pas

- $P_{circuit}(\beta) = P_{circuit}$

- Cette stratégie est particulièrement pour les processeurs de serveurs:

- La puissance de calcul profite de l'augmentation de fréquence

- La puissance de calcul profite de l'augmentation du parallélisme

#### Dans la pratique

Les vitesses maximum stagnent depuis le début des années 2000 (3 à 4 Ghz) à cause des problèmes de dissipation thermique.

#### Dans la pratique

- Les vitesses maximum stagnent depuis le début des années 2000 ( 3 à 4 Ghz) à cause des problèmes de dissipation thermique.

- On ne peut diminuer sans cesse la tension d'alimentation sans s'éloigner du modèle d'interrupteur idéal : les circuits ont des courants de fuite de moins en moins négligeables

#### Dans la pratique

- Les vitesses maximum stagnent depuis le début des années 2000 ( 3 à 4 Ghz) à cause des problèmes de dissipation thermique.

- On ne peut diminuer sans cesse la tension d'alimentation sans s'éloigner du modèle d'interrupteur idéal : les circuits ont des courants de fuite de moins en moins négligeables

- Les technologues doivent jongler avec des procédés de fabrication de plus en plus complexes pour continuer à suivre la "loi de Moore".

#### Dans la pratique

- Les vitesses maximum stagnent depuis le début des années 2000 ( 3 à 4 Ghz) à cause des problèmes de dissipation thermique.

- On ne peut diminuer sans cesse la tension d'alimentation sans s'éloigner du modèle d'interrupteur idéal : les circuits ont des courants de fuite de moins en moins négligeables

- Les technologues doivent jongler avec des procédés de fabrication de plus en plus complexes pour continuer à suivre la "loi de Moore".

- On a plusieur fois prédit la fin de la loi de Moore pour des raisons "scientifiques" (physique du transistor) mais il semble en 2014 que le plus grave problème soit économique...

## **Evolution technologique**

La fin de la loi de Moore ?