# **AN10DS40** Preliminary Information

# Development System for AN10E40 FPAA Firmware Version 1.0

Anadigm was pleased to present the design community with the world's first true programmable analog array, the AN10E40. We coupled this array offering with a unique design system called AnadigmDesigner; supported with an extensive collection of analog circuit building blocks called IPmodules<sup>™</sup>. This triad of technology represents a powerful analog design environment for the designer with minimal analog knowledge. For the system designer, Anadigm is pleased to present the Anadigm programmable analog solution in a context that will allow you to leverage your strengths in processor/controller based system design.

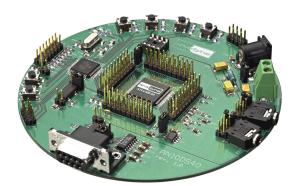

The AN10DS40 development system provides a complete and easy to use platform that allows you to easily investigate the benefits of field programmable, reconfigurable analog technology coupled with host processors/controllers. The system centers on the AN10E40 Field Programmable Analog Array (FPAA) and demonstrates how simple its connection to a companion microprocessor is. Stable, drift free analog circuits that can be reconfigured on the fly by companion logic in a killer combination of technologies that will "extend the boundaries of digital systems".

Out of the box, the AN10DS40 is ready to serve you in a number of ways. The companion microprocessor holds four FPAA configurations in its on-chip Flash memory. Simply power the board up, and hit one of the four configuration buttons to instantly configure the AN10E40 FPAA. Using an oscilloscope, you'll be able to quickly see the AN10E40 in action.

Connect the AN10DS40 FPAA development board via your PC's RS-232 port to AnadigmDesigner and you are ready to download your own designs directly to the FPAA. You may also download to the microprocessor's Flash memory for later stand alone operation, just described above. As your system design progresses to the prototyping phase, the AN10DS40 can also connect to your target system and serve as the download conduit.

Advanced users may elect to drive the AN10DS40 with an RS-232 host of their own design or drive it with a standard SPI master. The "next level" engineer will quickly realize the power of a tightly coupled host processor and start writing his own code. We encourage this exploration of the technologies, and have equipped you to do so. The schematic and source listing are both made available so you can use the AN10DS40 as the reference starting point that will quickly jumpstart your own designs.

# The Major Features

- Investigate Microcontroller and FPAA Coprocessing

- Use as a Stand Alone FPAA Evaluation Platform

- Four FPAA Configurations Held in Flash

- Can be used with Standard Serial PROMs

- Connects to AnadigmDesigner via RS-232

- · Connect to any SPI Master or RS-232 Host

- Can be Used to Configure Your Target System

- Speedy Downloads

- Full Source Code Included

- Schematics Included

Anadigm reserves the right to make any changes without further notice to any products herein. Anadigm makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Anadigm assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including with limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Anadigm does not convey any license under its patent rights nor the rights of others. Anadigm products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Anadigm product could create a situation where personal injury or death may occur. Should buyer purchase or use Anadigm product for any such unintended or unauthorized application, buyer shall indemnify and hold Anadigm and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Anadigm was negligent regarding the design or manufacture of the part.

> © Anadigm Ltd. 2000 © Anadigm Inc. 2000 All Rights Reserved.

# **Table of Contents**

| Development System Overview                                | 1      |

|------------------------------------------------------------|--------|

| What does the development system do?                       |        |

| Stand Alone Operation                                      |        |

| Hosted by AnadigmDesigner                                  | 1      |

| Ready for your custom application                          | 1      |

| Now for the really good part                               | 1      |

| A quick explanation of what is on board                    | 2      |

| Connecting Power                                           | 3      |

| Stand Alone Operation                                      |        |

| Configuration 1 - Emergency Broadcast System Alert Tone    | 3      |

| Configuration 2 - Gain Stage of 5                          |        |

| Configuration 3 - In Phase Music Cancellation              |        |

| Configuration 4 - C Weighted Filtering                     | 4      |

| Using a Serial EPROM                                       |        |

| Connecting Up To AnadigmDesigner                           |        |

| The physical connection                                    |        |

| The download procedure                                     |        |

| Development System Board Details                           |        |

| Switches                                                   |        |

| Push Button Switches S1 through S4                         |        |

| Push Button Switch S5 Reset                                |        |

| Push Button Switch S6 IRQ                                  |        |

| Connectors                                                 |        |

| P1 - External Push Button Interface                        |        |

| P2 - External Target Array Interface                       |        |

| P3 - External SPI Master Interface                         |        |

| P7 - Top Side AN10E40 Signals                              |        |

| P8 - Right Side AN10E40 Signals                            |        |

| P9 - Bottom Side AN10E40 Signals                           |        |

| P9 - Dollotti Side AN10E40 Signala (Canfiguration)         | 0<br>0 |

| P10 - Left Side AN10E40 Signals (Configuration)<br>Jumpers | 0      |

| J1 - Off Board Target Enable                               |        |

| J2 - Factory Reserved, Flash Restoration                   |        |

| J3 - On Board Clock Resource                               |        |

| J4 - Microcontroller CLKOUT Enable                         |        |

| J5 - DCE vs. DTE Configuration Block                       |        |

| J6 - Factory Reserved, Flash Restoration                   |        |

| J7 - On Board Voltage Regulator Enable                     |        |

| J8 - Serial EPROM Enable                                   |        |

|                                                            |        |

| J10 - Stereo Jack Output & Configuration Block             |        |

| J12 - Stereo Jack Input & Configuration Block              |        |

| J13 - Enable External VMR Source.                          | 10     |

| AN10E40 Package to Board Signal Cross Reference            |        |

| Downloading to your Target System                          |        |

| Advanced User Topics.                                      |        |

| The Microcontroller's Memory Map                           |        |

| High Level View - The Complete Memory Map                  |        |

| IO and RAM                                                 |        |

| FPAA Configuration Files                                   |        |

| User Playground                                            |        |

|                                                            |        |

| Protected ABK                                              |        |

| Status, Control, Monitor ROM and ISR Vectors               |        |

| Firmware Overview                                          |        |

| Anadigm Boot Kernal (ABK)                                  |        |

| IDLE State                                                 | 18     |

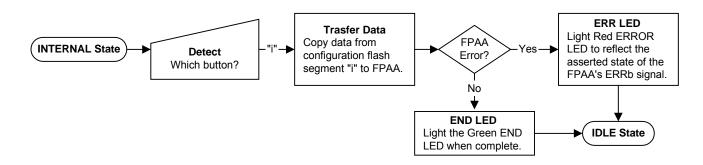

| INTERNAL State                                                      | 18 |

|---------------------------------------------------------------------|----|

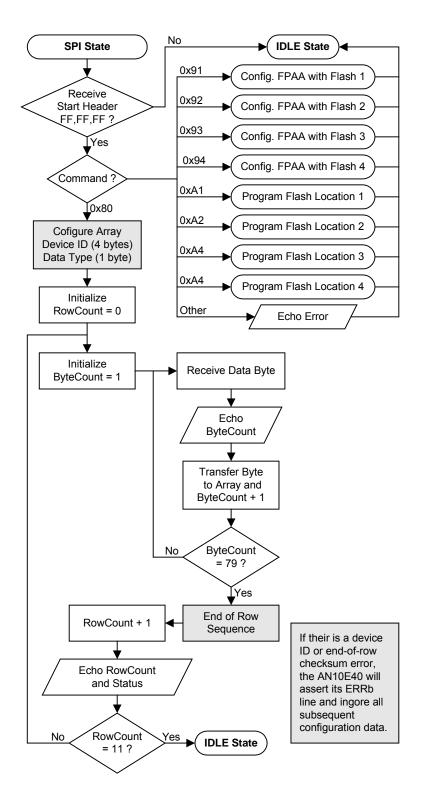

| SPI State                                                           |    |

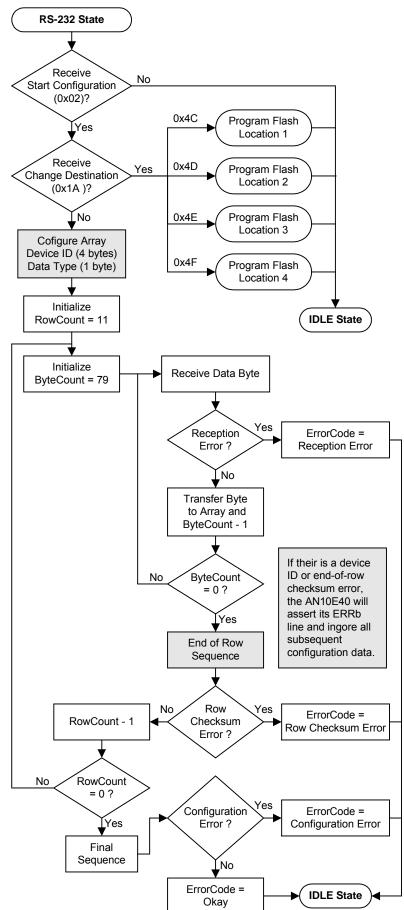

| RS-232 State                                                        |    |

| ABK Boot                                                            |    |

| H - Help                                                            |    |

| W - Wipe                                                            |    |

| P - Program                                                         |    |

| U - Update                                                          |    |

| X - Exit                                                            |    |

| Configuration Bit Streams - AHF Format                              |    |

| Connecting to an RS-232 Host.                                       |    |

| The physical connection                                             |    |

|                                                                     |    |

| Special Command Headers for RS-232 Routed Configuration Bit Streams |    |

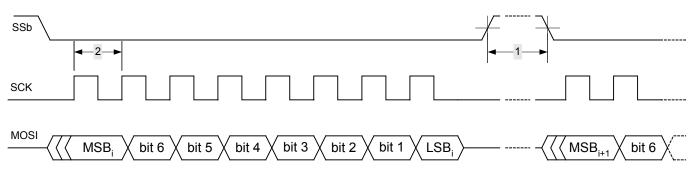

| The logical connection<br>Connecting to a SPI Master                |    |

|                                                                     |    |

| The physical connection                                             |    |

| Special Command Headers for SPI Routed Configuration Bit Streams    |    |

| The logical connection                                              |    |

| Appendix A - Source File Descriptions                               |    |

| Appendix B - Motorola S-Record Format                               |    |

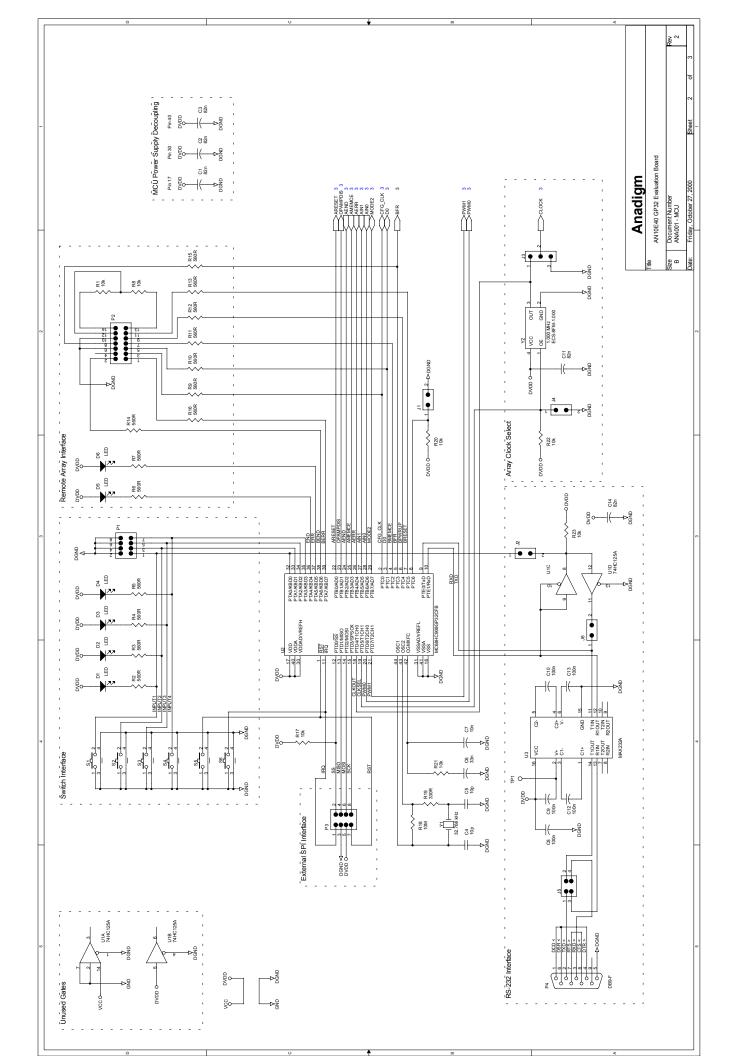

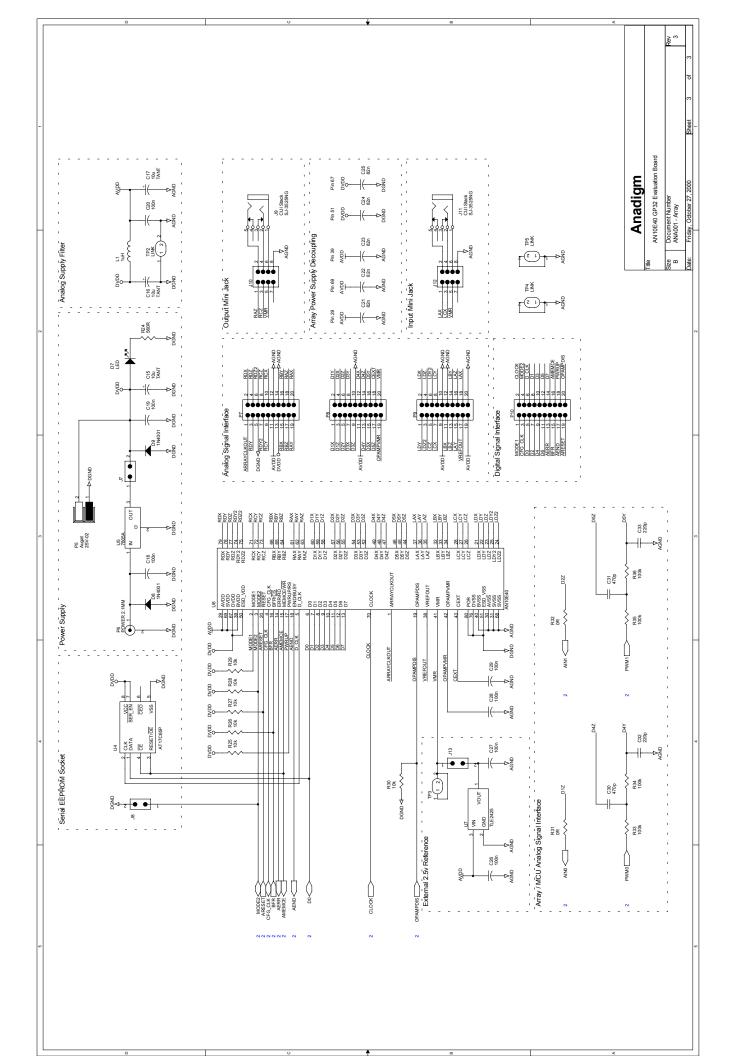

| Appendix C - Board Schematic                                        |    |

|                                                                     |    |

# Development System Overview

# What does the development system do?

The development system demonstrates the easy pairing of an AN10E40 field programmable analog array (FPAA) with a microcontroller. The system is designed with resources that facilitate: stand alone operation, connection to AnadigmDesigner software, and connection to a target FPAA system.

### Stand Alone Operation

Out of the box, the AN10DS40 is ready to demonstrate the AN10E40 FPAA. The on board microcontroller has 4 FPAA configurations stored in its on chip Flash memory. Simply power the board up (+8 to +12 VDC on the center post of P6), then hit one of the S1 through S4 pushbutton switches. Nearly instantly, the micro configures the FPAA and releases it for immediate operation.

The second stand alone function takes the microcontroller out of the picture, and lets the FPAA load up a configuration pattern under its own control out of reset. Placing a shorting block on J8 instructs the microcontroller to allow the FPAA to configure itself using the configuration contained in the serial EPROM socket (U4).

The stand alone operations are handy for quick demonstrations to your colleagues, and serves as an effective demonstration of the ease and speed of connection between Anadigm FPAA's and standard logic. However, when it comes to investigating the behavior of the AN10E40 device itself, you will soon want to connect the development system up to AnadigmDesigner.

### Hosted by AnadigmDesigner

The AN10DS40 has a standard 9 pin RS-232 connector that allows quick connection to your PC. The FPAA design software AnadigmDesigner is design system aware. Downloading your experimental circuit configurations to the development system is simply a matter of making a single menu selection. On command, AnadigmDesigner will download the current configuration to the on board AN10E40, or to one of the four Flash memory configuration regions within the microcontroller (for latter stand alone demonstration).

As your design progresses, you may want to boot FPAA's in your own target system rather than on the AN10DS40 board; no problem. Shorting the J1 jumper, instructs the microcontroller to redirect configuration signals to the External Target Interface (P2).

### Ready for your custom application

The AN10DS40 is ready for your own custom tasks. In addition to the functionality described above, the AN10DS40 is also ready to serve as a SPI Slave. A simple connection to any SPI Master system, and that system is ready to take control of downloads to the FPAA. The schematics, file formats and everything else you need to know to successfully communicate with the AN10DS40 through either its SPI or RS-232 ports is included in this document.

### Now for the really good part...

Once you've gotten your feet wet, and begun to understand the power of programmable analog, we'd like to encourage you to transcend this first level and move on to the real power domain. This is where your logic works in concert with the FPAA. In this system environment, analog configurations are continuously swapped or adjusted under control of conventional logic. Leaving the static configuration paradigm behind, will allow you to build incredibly capable systems with unheard of efficiency. Anadigm is here to support you. Keep tabs on the website (http://www.anadyne-micro.com) for releases of the complete Anadigm Boot Kernel (ABK) library. We will provide you the connection points to software that allows you to concentrate on the power of the analog array, without having mess with the details of configuration communications.

1

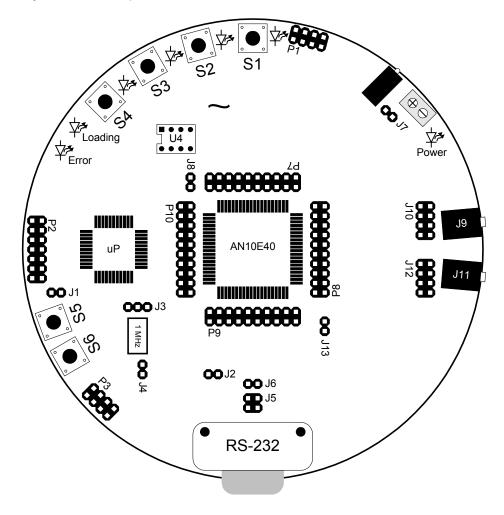

# A quick explanation of what is on board

Starting at 6 o'clock and working our way around clockwise, we first see a standard 9 pin RS-232 connector. Just behind the connector is jumper block J5, that allows the port to present itself either as a DCE or DTE interface. For the most common PC and cable combinations, the factory setting of DCE works fine.

P3 is a SPI port connection. Out of reset the design system watches for RS-232, SPI or push button activity. The design system is configures as a SPI slave. Any standard SPI master can talk directly to the AN10DS40 with no need for jumper setting or code changes.

IRQ and RESET buttons are provided. The reset button does the obvious thing, it resets the AN10DS40 back to its power up reset state. The IRQ button will cause an ABORT interrupt service routine to run. No matter what the AN10DS40 happens to be doing at the moment, pressing the IRQ button will take the ABK back to the IDLE state.

the 14 pin P2 connector brings a set of FPAA configuration signals off the board to facilitate connection to your own target system. Shorting jumper J1 causes the microcontroller to re-route configuration signals from the on board FPAA to this External Target Array interface.

The upper left quadrant of the board is occupied by 4 push button switches. Hitting any one of these 4 buttons tells the microcontroller to download the associated pre-stored configuration to the FPAA (either on board of to the target system). Adjacent to the switches is the P1 connector, which brings the pushbutton signals to a hand connector. A logic signal can be used to emulate a button press.

The P6 connector allows connection of any regulated 8-12 VDC power supply. Behind P6 is a 5 volt linear regulator. A pair of screw terminals is also provided if you should desire to bypass the on board voltage regulator (open jumper J7) and connect your own power.

J9 and J11 provide hand mini-stereo jacks for output and input respectively. Jumper blocks J10 and J12 allow for connection options.

Moving to the center of the board is the AN10E40 array itself with every pin connected up to a header for easy access. Please consult the AN10E40 data manual for a detailed description of the FPAA device.

Moving left again, is a Motorola MC68HC908 microcontroller. The logic portion of the board handles SPI, pushbutton and RS-232 communications tasks. It sources two sets of FPAA configuration signals. The first set is directed to the on chip AN10E40 array, the second set is directed to the External Target Array interface P2.

There are multiple options for driving a clock to the FPAA, the details of which are described below. The default jumper settings connect an on board 1MHz oscillator to the AN10E40's clock input.

There is one Green LED associated with each of the four configuration pushbutton switches. If the switch line goes low by either the button or its associated logic line on the P1 header, the LED will light.

A steady Yellow LED adjacent to the power connectors indicates that the board is powered up.

There are two other LED's that reflect that state of the FPAA's END and ERRb signals. If the array encounters an error during configuration, the download will be aborted, it will drop its ERRb signal, and the Red Error LED will light. This condition will remain until either a reset signal is asserted or until a new download is started.

The FPAA drops its END signal low during configuration, this will cause the Yellow Loading LED to light. This LED only stays light as long as the FPAA is configuring. Since this usually happens so quickly, it may appear as just a brief flicker.

# **Connecting Power**

There are two options for establishing a power connection to the design system:

- 1. Connect +8 to +12 VDC to the center post of the 2.1mm jack P6 (GND to its sleeve) and leave J7 in place. The on board linear regulator will drop the voltage down to +5 VDC.

- 2. Remove the J7 jumper, and supply your own regulated +5VDC to adjacent screw terminals. A 3/4 amp in-line fuse is recommended.

# Stand Alone Operation

Out of the box, the AN10DS40 is ready to begin work. With board power connected, just hit one of the four pushbutton switches, S1 through S4. The microcontroller will proceed to transfer a configuration image from the appropriate region of its on chip Flash to the on board FPAA. (Shorting jumper J1 will instead direct the configuration data stream to go to the P2 External Target Array interface.)

### **Configuration 1 - Emergency Broadcast System Alert Tone**

The US Emergency Broadcast System was established in 1963 in order to provide a country wide civil communications network. Cooperating radio and television stations air a long alert tone before broadcasting the important information. The alert tone is specified as the sum of 853Hz with 960Hz sinusoidal waveforms. This tone resonates most small speaker systems well, is well within the bandwidth of the broadcasting channels and meets the important requirement that it be pretty darn annoying to listen to.

| Recommended Equipment | Amplified Stereo Speakers                                                          |                                                                   |  |

|-----------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------|--|

|                       | Oscilloscop                                                                        | De                                                                |  |

| Input Channels        | <b>None</b> This demonstration circuit uses oscillator IPmodules to generate the   |                                                                   |  |

|                       | two fundamental tones and a summing amplifier to combine them.                     |                                                                   |  |

| Output Channels       | P7-17 853Hz Sinusoid                                                               |                                                                   |  |

|                       | P7-4 960Hz Sinusoid                                                                |                                                                   |  |

|                       | <b>P7-8&amp;18</b> Sum of the above two signals. (Tip and Ring of stereo jack J9.) |                                                                   |  |

|                       | J9                                                                                 | A convenient output jack to plug in a pair of amplified speakers. |  |

### Configuration 2 - Gain Stage of 5

The final configuration is a simple gain stage with the gain value set to 5. The Input and Output connections are the same as Configurations 2 and 3. Taken together, these 3 configurations then provide a set of circuits that can be very quickly switched in and out of operation, demonstrating on the fly reconfiguration potential of the AN10E40.

| Recommended Equipment | Network Analyzer, or                                                       |                                                                   |  |

|-----------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------|--|

|                       | Oscilloscope and Audio Frequency Sweep Generator                           |                                                                   |  |

| Input Channels        | J11 or Apply the (AC coupled) Network Analyzer or Sweep Generator's        |                                                                   |  |

|                       | <b>P9-7&amp;18</b> outputs up to the Tip and Ring of J11                   |                                                                   |  |

| Output Channels       | <b>P7-8&amp;18</b> Sum of the two signals (Tip and Ring of stereo jack J9) |                                                                   |  |

|                       | J9                                                                         | A convenient output jack to plug in a pair of amplified speakers. |  |

### **Configuration 3 - In Phase Music Cancellation**

When listening to he world around you, most low frequency noise (or music, or someone else's music that you consider to be noise) reaches your ears roughly in phase. The low frequencies of sound have a longer wavelengths then higher frequencies. Consequently, for low frequency signals (signals in which the sound's wavelength is considerably larger than the distance between your two ears) will arrive at each of your ears roughly in phase. Higher frequency sounds on the other hand are much more likely to arrive at your two ears out of phase. It is this phase difference that allows us to "locate" a sound. This bit of physiology is taken advantage of in the design of surround sound music systems.

In this interesting demonstration, you supply the AN10E40 with a music signal (a portable CD player usually works very well for this). The circuit adds the left channel to the inverted version of the right channel, provides some gain and outputs it for your observation. The signal is a difference of the left and right channels, and is an demonstrates the content of "music" that allow you directionally locate a sound source.

| Recommended Equipment | Amplified Stereo Speakers                                                |                                                  |  |  |

|-----------------------|--------------------------------------------------------------------------|--------------------------------------------------|--|--|

|                       | CD Player                                                                |                                                  |  |  |

|                       | Mini-Stereo Plug to Mini-Stereo Plug cable                               |                                                  |  |  |

| Input Channels        | J11 Using the mini-plug to mini-plug cable, connect the output of the CD |                                                  |  |  |

|                       | player to the AN10DS40 input jack.                                       |                                                  |  |  |

| Output Channels       | P7-8&18 Tip and Ring of J9                                               |                                                  |  |  |

|                       | J9 A convenient output jack to plug in a pair of amplified speakers. The |                                                  |  |  |

|                       |                                                                          | difference signal is presented on both channels. |  |  |

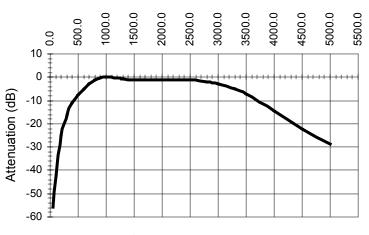

## **Configuration 4 - C Weighted Filtering**

Without diving too deeply into the history and detailed use of C Weighted filtering, this filter specification (shown below) is commonly used for testing audio systems and environments in which human hearing is concerned.

Frequency (Hz)

C Weighted Filter

Passing an audio signal through the AN10E40 with this configuration image loaded will result in an output signal in which the tonal quality is something akin to AM radio or a telephone. While the signal may no longer be very pleasant to listen to, the point of the demonstration is that filters can be easily constructed in the AN10E40 to meet almost any arbitrary set of specifications.

| Recommended Equipment | Network Analyzer, or                                                       |                                                                   |  |

|-----------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------|--|

|                       | Oscilloscope and Audio Frequency Sweep Generator                           |                                                                   |  |

| Input Channels        | J11 or Apply the (AC coupled) Network Analyzer or Sweep Generator's        |                                                                   |  |

|                       | P9-7&18 outputs up to the Tip and Ring of J11                              |                                                                   |  |

| Output Channels       | <b>P7-8&amp;18</b> Sum of the two signals (Tip and Ring of stereo jack J9) |                                                                   |  |

|                       | J9                                                                         | A convenient output jack to plug in a pair of amplified speakers. |  |

The network analyzer will demonstrate the response of the circuit with a plot that looks like the above figure. If you are not fortunate enough to have a network analyzer, driving the input with an audio frequency sweep generator and watching the output on an oscilloscope (with the horizontal sweep speed the same as, and triggered by, the sweep generator) will give you a good feeling for the behavior of the circuit.

### Using a Serial EPROM

Placing a shorting block on jumper J8 instructs the microcontroller to allow the on board AN10E40 to source its own configuration clock, and pull data directly out of the serial EPROM installed in socket U4. With all the focus of letting a micro handle the configuration tasks, you may need to be reminded that the AN10E40 is perfectly well suited to performing as a stand alone component. With a standard serial EPROM adjacent, the FPAA has its own configuration engine that allows it to automatically download a configuration image out of reset. The serial EPROM socket provided on the AN10DS40 board allows this to be demonstrated. Please note, that this particular boot method is only applicable to the on board FPAA. The J1 jumper setting is ignored.

# Connecting Up To AnadigmDesigner

After you've messed around with the design system board a bit using its stand alone features, you'll soon want to connect up to AnadigmDesigner and start downloading your own configurations. The AN10DS40's RS-232 port is designed to make this connection as quick and trouble free as possible.

### The physical connection

With the J5 block set to DCE configuration (1 shorted to 2, and 3 shorted to 4) most PC and serial cable combinations hook up just fine. AnadigmDesigner has options for setting up which of your PC's serial ports will be used. The firmware sets up the microcontroller to receive data at 9600 Baud, no start bits, 1 stop bit, 8 bits of data, no parity. If you have a non-standard serial cable, all that may be necessary to establish the connection is to configure the AN10DS40 to present itself as DTE (using J5, short 1 to 3, and 2 to 4).

### The download procedure

From the AnadigmDesigner pull down menu "Configure", you will see choices for downloading the currently loaded circuit either directly to an FPAA or to one of the 4 Flash memory regions within the microcontroller. Downloading to the microcontroller's Flash allows for later stand alone (disconnected from the PC) operation. During the download, the Yellow LED will light, indicating that the download is in progress. In the unlikely even that any error is encountered by the FPAA which prevents the successful download, the Red LED will light, signifying an error condition. The ERROR LED will remain on until either a reset is asserted or a new download attempt made.

**Note** - As soon as you direct AnadigmDesigner to download to one of the configuration segments of the microcontroller's Flash memory, the old contents of that segment of memory will be lost. Please see the section ABK\_Boot to understand how to restore your AN10DS40 to its as-first-shipped condition.

# Development System Board Details

The AN10DS40 has everything you need to investigate the use of an AN10E40 FPAA as a peripheral to a microprocessor or as a stand alone device. The board has switches, connectors and sockets suitable for demonstration many of the devices possible uses.

## Switches

### Push Button Switches S1 through S4

As shipped from the factory, the AN10DS40 is ready to demonstrate the versatility of the AN10E40 FPAA. Simply power the board up and hit any one of the S1 through S4 switches. Nearly instantly, the microcontroller passes a segment of its Flash memory down to the AN10E40. After this very brief configuration sequence, the AN10E40 will be operating using the configuration associated with that section of Flash associated with the button pressed.

The P1 connector is wired in parallel to these 4 switches, allowing your own off board logic to emulate the closing of these 4 switches.

## Push Button Switch S5 Reset

Pressing S5 resets the on board microcontroller, bringing the entire system back to its power on reset state. Access to this same RST signal is also provided on the P3 SPI connector.

7

### Push Button Switch S6 IRQ

Pressing S6, causes the IRQb pin on the on board microcontroller to go low. As shipped from the factory, this runs and Abort routine. No matter what the processor happens to be doing at the moment, control is passed back to the ABK's IDLE mode. It is also available as a user feature for those advanced users wishing to use an interrupt for some custom functionality. Access to this same IRQ signal is also provided on the P3 SPI connector.

# **Connectors**

For all two row "P" and "J" connectors, pin numbering increases up from the indicated Pin 1 in a zig-zag fashion, as shown in the tables presented below.

### P1 - External Push Button Interface

| Signal Name |   |   | Signal Name |                                                         |

|-------------|---|---|-------------|---------------------------------------------------------|

| INPUT1      | 1 | 2 | DGND        | Applying a logic low to any of the INPUT[1:4] pins will |

| INPUT2      | 3 | 4 | DGND        | have the same effect as manually pressing the           |

| INPUT3      | 5 | 6 | DGND        | normally open switches S1-S4. Logic driving these       |

| INPUT4      | 7 | 8 | DGND        | pins should be able to sink 8mA.                        |

### P2 - External Target Array Interface

| Signal Name |    |    | Signal Name |                                                        |

|-------------|----|----|-------------|--------------------------------------------------------|

| ERRb        | 1  | 2  | END         | Connector P2 allows a direct connection to a target    |

| CFG_CLK     | 3  | 4  | DCLK        | system other than the EVM (be sure to short jumper     |

| D0          | 5  | 6  | DGND        | J1). Please consult the AN10E40 data manual for the    |

| MEMCEb      | 7  | 8  | BFRb        | complete functional description of these signals.      |

| PWRUP       | 9  | 10 | DGND        | Generally speaking, 1 for 1 connection of these        |

| RESETb      | 11 | 12 | DVDD        | signals to the target system's FPAA is all that is     |

| MODE1       | 13 | 14 | MODE2       | required to utilize P2 as a target configuration port. |

### P3 - External SPI Master Interface

| Signal Name |   |   | Signal Name |                                                        |

|-------------|---|---|-------------|--------------------------------------------------------|

| IRQb        | 1 | 2 | SSb         | Connector P3 accommodates connection of an             |

| DGND        | 3 | 4 | MISO        | external SPI master; the AN10DS40 board serving as     |

| DVDD        | 5 | 6 | MOSI        | a SPI slave. Details of the SPI signaling are given in |

| RSTb        | 7 | 8 | SCK         | the section below, Connecting to a SPI Master.         |

### P7 - Top Side AN10E40 Signals

| Signal Name |    |    | Signal Name |                                                         |

|-------------|----|----|-------------|---------------------------------------------------------|

| ARRAYCLKOUT | 1  | 2  | RDX         | Connectors P7, P8 and P9 provide easy access            |

| RDY         | 3  | 4  | RDZ         | points to the AN10E40's analog IO X, Y & Z signals.     |

| DGND        | 5  | 6  | RDZ2        |                                                         |

| RDY2        | 7  | 8  | RCZ         | AVDD supply is a filtered version of DVDD. AGND is      |

| RCY         | 9  | 10 | RCX         | the same electrical node as DGND, but there are only    |

| AVDD        | 11 | 12 | AGND        | a few discrete connections between the two power        |

| DVDD        | 13 | 14 | AGND        | planes to ensure optimal digital noise isolation to the |

| RBX         | 15 | 16 | RBY         | analog circuitry. ARRAYCLKOUT reflects one of the       |

| RBZ         | 17 | 18 | RAZ         | AN10E40's internal analog clocks, as programmed by      |

| RAY         | 19 | 20 | RAX         | the user.                                               |

| Signal Name |    |    | Signal Name |                                                           |

|-------------|----|----|-------------|-----------------------------------------------------------|

| D1X         | 1  | 2  | D1Y         | Connectors P7, P8 and P9 provide easy access              |

| D1Z         | 3  | 4  | D2X         | points to the AN10E40's analog IO X, Y & Z signals.       |

| D2Y         | 5  | 6  | D2Z         |                                                           |

| D3X         | 7  | 8  | D3Y         | OPAMPVMR should neither be loaded or driven, it           |

| D3Z         | 9  | 10 | AGND        | simply serves as a bypass point for the Voltage Mid-      |

| AVDD        | 11 | 12 | D4X         | Rail signal for the array's amplifiers. Similarly CEXT is |

| D4Y         | 13 | 14 | D4Z         | only a bypass point for the array's internal voltage      |

| D5X         | 15 | 16 | D5Y         | reference generator. VMR signal is provided for           |

| D5Z         | 17 | 18 | CEXT        | monitoring. If J13 is removed, an externally supplied     |

| OPAMPVMR    | 19 | 20 | VMR         | VMR signal can be applied on this pin or on J13-1.        |

# P9 - Bottom Side AN10E40 Signals

| Signal Name |    |    | Signal Name |                                                     |

|-------------|----|----|-------------|-----------------------------------------------------|

| LDY         | 1  | 2  | LDX         | Connectors P7, P8 and P9 provide easy access        |

| LDZ2        | 3  | 4  | LDZ         | points to the AN10E40's analog IO X, Y & Z signals. |

| LCZ         | 5  | 6  | LDY2        |                                                     |

| LCX         | 7  | 8  | LCY         | VREFOUT provides a convenient test point for        |

| AVDD        | 9  | 10 | AGND        | monitoring the FPAA's internal reference voltage.   |

| LBX         | 11 | 12 | AGND        |                                                     |

| LBZ         | 13 | 14 | LBY         |                                                     |

| LAY         | 15 | 16 | LAZ         |                                                     |

| VREFOUT     | 17 | 18 | LAX         |                                                     |

| AVDD        | 19 | 20 | AGND        |                                                     |

# P10 - Left Side AN10E40 Signals (Configuration)

| Signal Name |    |    | Signal Name |                                                       |

|-------------|----|----|-------------|-------------------------------------------------------|

| MODE1       | 1  | 2  | CLOCK       | The P10 connector gives direct access to the          |

| CFG_CLK     | 3  | 4  | MODE2       | AN10E40's configuration interface.                    |

| D0          | 5  | 6  | D_CLK       |                                                       |

| D2          | 7  | 8  | D1          | For a complete description of the function and timing |

| D4          | 9  | 10 | D3          | of these signals, please reference the AN10E40 data   |

| D6          | 11 | 12 | D5          | manual.                                               |

| ERRb        | 13 | 14 | D7          |                                                       |

| BFRb        | 15 | 16 | MEMCEb      |                                                       |

| END         | 17 | 18 | PWRUP       |                                                       |

| RESETb      | 19 | 20 | OPAMPDIS    |                                                       |

# Jumpers

For all two row "P" and "J" connectors, pin numbering increases up from the indicated Pin 1 in a zig-zag fashion, as shown in the tables presented below.

# J1 - Off Board Target Enable

Signal Name

| PTC6 | 1 | Normally Open - Leaving J1 open tells the ABK that the target FPAA is on board. |

|------|---|---------------------------------------------------------------------------------|

| DGND | 2 |                                                                                 |

|      |   | Shorting J1 informs the ABK that the target FPAA is off board. If shorted, all  |

|      |   | configuration signals are routed to the P2 target system interface connector    |

9

### J2 - Factory Reserved, Flash Restoration

Signal Name

| Factory Reserved | 1 | Normally Open - Leave J2 open during normal operation.                            |

|------------------|---|-----------------------------------------------------------------------------------|

| Factory Reserved | 2 |                                                                                   |

|                  |   | Shorting J2 should only be done during Flash restoration, please see the section, |

|                  |   | Rebuilding the AN10DS40 back to Factory Contents.                                 |

### J3 - On Board Clock Resource

Signal Name

| (uP)CLKOUT   | 1 |

|--------------|---|

| (FPAA) CLOCK | 2 |

| DGND         | 3 |

|              |   |

**Normally 1& 2 are Shorted** - This allows either the on board 1 MHz oscillator (J4 Open) or the microcontroller (J4 Shorted) to drive the AN10E40's CLOCK signal.

Removing the shorting block allows you to drive 2 using an external signal generator (using 3 as a return ground).

### J4 - Microcontroller CLKOUT Enable

Signal Name

| CLKSEL | 1 | Normally Open - Leaving J4 open instructs the microcontroller to disable its      |

|--------|---|-----------------------------------------------------------------------------------|

| DVDD   | 2 | CLKOUT signal, allowing the 1 MHz on board oscillator to provide the clock to the |

|        |   | AN10E40.                                                                          |

|        |   |                                                                                   |

|        |   | Shorting J4 disables the 1 MHz on board oscillator output and instructs the       |

|        |   | microcontroller to drive the FPAA CLOCK signal using its CLKOUT signal.           |

# J5 - DCE vs. DTE Configuration Block

| Signal Name |     |   |   | Signal Name |                                                                                                                                                                                   |

|-------------|-----|---|---|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | TXD | 1 | 2 | TOUT        | Normal (DCE) Configuration:                                                                                                                                                       |

|             | RIN | 3 | 4 | RXD         | 1 shorted to 2                                                                                                                                                                    |

|             |     |   |   |             | 3 shorted to 4                                                                                                                                                                    |

|             |     |   |   |             | In the normal configuration, this presents the AN10DS40's RS-232 port as DCE. This is the configuration compatible with most PC's and commons serial port cables.                 |

|             |     |   |   |             | DTE Configuration:<br>1 shorted to 3<br>2 shorted to 4<br>In the DTE configuration, the RS-232 Tx and Rx lines<br>are crossed before going to the AN10DS40's<br>transceiver chip. |

### J6 - Factory Reserved, Flash Restoration

Signal Name

| Factory Reserved | 1 | Normally Open - Leave J6 open during normal operation.                            |

|------------------|---|-----------------------------------------------------------------------------------|

| Factory Reserved | 2 |                                                                                   |

|                  |   | Shorting J6 should only be done during Flash restoration, please see the section, |

|                  |   | Rebuilding the AN10DS40 back to Factory Contents                                  |

## J7 - On Board Voltage Regulator Enable

### Signal Name

| olghai Naine       |   |                                                                                                          |

|--------------------|---|----------------------------------------------------------------------------------------------------------|

| Volt Regulator Out | 1 | Normally Shorted - Shorting J7 connects the output of the on board voltage                               |

| DVDD               | 2 | regulator to the board's DVDD power plane. In order for things to work correctly,                        |

|                    |   | you'll of course need to supply between 8 and 12 Volts DC to P6 (center post is +).                      |

|                    |   | If J7 is open, the user is expected to supply a clean will regulated 5V DC to the screw terminals on P5. |

## J8 - Serial EPROM Enable

Signal Name

| MODE2 | 1 | Normally Open - Leave J8 open during normal operation.                       |

|-------|---|------------------------------------------------------------------------------|

| DGND  | 2 |                                                                              |

|       |   | Shorting J8 allows the on board AN10E40 to boot from the serial EPROM socket |

|       |   | U4. The ABK detects this signal being low, and gets out of the way.          |

# J10 - Stereo Jack Output & Configuration Block

| Signal Name |     |   |   | Signal Name     |                                                                                                                                                                                                                                                                                                                                                               |

|-------------|-----|---|---|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | RAZ | 1 | 2 | LEFT OUT (ring) | Normal Configuration:                                                                                                                                                                                                                                                                                                                                         |

|             | RCZ | 3 | 4 | RIGHT OUT (tip) | 1 shorted to 2                                                                                                                                                                                                                                                                                                                                                |

|             | VMR | 5 | 6 | GND (sleeve)    | 3 shorted to 4                                                                                                                                                                                                                                                                                                                                                |

|             |     | 7 | 8 | AGND            | 6 shorted to 8                                                                                                                                                                                                                                                                                                                                                |

|             |     |   |   |                 | In the normal configuration, AGND is used as the ground reference to the signals being presented to the mini stereo plug J9.<br>5 shorted to 6<br>In this alternate configuration, VMR is instead passed as the ground reference to J9. This is not a typically recommended configuration. The VMR output is not designed to source or sink any load current. |

# J12 - Stereo Jack Input & Configuration Block

| Signal Name |     |   |   | Signal Name    |                                                                                                                                                                    |

|-------------|-----|---|---|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | LAX | 1 | 2 | LEFT IN (ring) | Normal Configuration:                                                                                                                                              |

|             | LCX | 3 | 4 | RIGHT IN (tip) | 1 shorted to 2                                                                                                                                                     |

| \<br>\      | /MR | 5 | 6 | GND (sleeve)   | 3 shorted to 4                                                                                                                                                     |

|             |     | 7 | 8 | AGND           | 5 shorted to 6                                                                                                                                                     |

|             |     |   |   |                | In the normal configuration, VMR (typically 2.5V with respect to AGND) is used as the ground reference to the signals being presented to the mini stereo plug J11. |

|             |     |   |   |                | 6 shorted to 8<br>In this alternate configuration, AGND is instead<br>passed as the ground reference to J11.                                                       |

# J13 - Enable External VMR Source

| Signal Name        |   |                                                                                    |

|--------------------|---|------------------------------------------------------------------------------------|

| (FPAA) VMR         | 1 | Normally Open - Leave J13 open during normal operation.                            |

| External 2.5V Ref. | 2 |                                                                                    |

|                    |   | Shorting J13 allows you to use the AN10DS40's external 2.5V reference voltage to   |

|                    |   | drive the AN10E40's VMR rail. Be sure to disable the on-chip VMR in the particular |

|                    |   | FPAA configuration being used when this jumper is in place.                        |

# AN10E40 Package to Board Signal Cross Reference

The following table provides a quick cross reference between the AN10E40 package pins and the most commonly used board connections for access to those pins. For a more complete description of the connections, please see the board schematic in Appendix C.

The signal naming convention holds that active low signals are named with a "b" suffix.

| Board            | Pkg.     | Signal Name      | Туре     | Description                                                                     |

|------------------|----------|------------------|----------|---------------------------------------------------------------------------------|

| P7-1             | 1        | ARRAYCLKOUT      | Dig. Out | Programming allows one of the 4 internal clocks to be                           |

|                  |          |                  | _        | presented here.                                                                 |

| P10-1            | 2        | MODE[1]          | Dig. In  | Configuration mode control pin                                                  |

|                  |          |                  |          | 0 = Boot From Serial ROM (BFR)                                                  |

|                  |          |                  |          | 1 = Micro Peripheral Interface Mode                                             |

| P10-4            | 3        | MODE[2]          | Dig. In  | Configuration mode control pin                                                  |

| J8-2             |          |                  |          | 0 = Use Internal Clock (CFG_CLK is output, 1/8 internal                         |

| to<br>DGND       |          |                  |          | ring oscillator freq.)<br>1 = Use External Clock (CFG_CLK is clock input to the |

| DGND             |          |                  |          | configuration logic.)                                                           |

| P10-3            | 4        | CFG CLK          | Dig. I/O | Configuration logic clock                                                       |

|                  |          |                  | <b>J</b> | Direction controlled by MODE[2]                                                 |

| P10-6            | 5        | DCLK             | Dig. Out | SPROM Configuration clock output                                                |

|                  |          |                  | -        | 1/2 frequency of CFG_CLK.                                                       |

| P10-5            | 6        | DATA[0]          | Dig. I/O | Data pins used for loading configuration data. DATA[0] is                       |

| P10-8            | 7        | DATA[1]          | Dig. I/O | used for serial BFR mode, and the entire byte width is                          |

| P10-7            | 8        | DATA[2]          | Dig. I/O | used in Micro mode.                                                             |

| P10-10           | 9        | DATA[3]          | Dig. I/O |                                                                                 |

| P10-9            | 10       | DATA[4]          | Dig. I/O |                                                                                 |

| P10-12           | 11       | DATA[5]          | Dig. I/O |                                                                                 |

| P10-11           | 12       | DATA[6]          | Dig. I/O |                                                                                 |

| P10-14           | 13       | DATA[7]          | Dig. I/O |                                                                                 |

| P10-13           | 14       | F1 (ERRb, RDb)   | Dig. I/O | Configuration Function pins                                                     |

| P10-16           | 15       | F2 (MEMCEb, WRb) | Dig. I/O | (BFR Mode , Micro Mode)                                                         |

| P10-15           | 16       | F0 (BFRb, CSb)   | Dig. In  |                                                                                 |

| P10-18           | 17       | F3 (PWRUP, RS)   | Dig. In  |                                                                                 |

| P10-17<br>P10-20 | 18<br>19 | F4 (END, BUSYb)  | Dig. Out | On Amn diachta innut                                                            |

| P10-20           | 19       | OPAMP_DISABLE    | Dig. In  | Op-Amp disable input<br>(normally tied to Vss, not usually utilized in systems) |

|                  |          |                  |          | Takes precedence over BFR's PWRUP input and Micro's                             |

|                  |          |                  |          | Function Register Bit Position 4 (Analog Enable)                                |

|                  |          |                  |          | 0 = Analog circuitry enabled                                                    |

|                  |          |                  |          | 1 = Analog circuitry disabled                                                   |

| P10-19           | 20       | RESETb           | Dig. In  | Chip RESET                                                                      |

|                  |          |                  |          | Falling edge detected to start Reset                                            |

| P9-2             | 21       | IOLDX            | Ana. In  | Unbuffered Analog input                                                         |

| P9-1             | 22       | IOLDY            | Ana. In  | Buffered Analog input                                                           |

| P9-4             | 23       | IOLDZ            | Ana. Out | Buffered Analog output                                                          |

| P9-3             | 24       | IOLDZ2           | Ana. Out | Uncommitted op-amp output                                                       |

| P9-6             | 25       | IOLDY2           | Ana. In  | Uncommitted op-amp input                                                        |

| P9-5             | 26       | IOLCZ            | Ana. Out | Buffered op-amp output                                                          |

| P9-8             | 27       |                  | Ana. In  | Buffered Analog input                                                           |

| P9-7             | 28       | IOLCX            | Ana. In  | Unbuffered Analog input                                                         |

| AVDD             | 29       | AVDD             | Pwr/Gnd  | Analog VDD, 5 Volts                                                             |

|                  | 30       | AVSS             | Pwr/Gnd  | Analog VSS, 0 Volts                                                             |

| AGND             | 31       | SVSS             | Pwr/Gnd  | Substrate VSS, 0 Volts                                                          |

| P9-11            | 32       | IOLBX            | Ana. In  | Unbuffered Analog input                                                         |

| P9-14            | 33       | IOLBY            | Ana. In  | Buffered Analog input                                                           |

| 1 | 2 |

|---|---|

|   |   |

| P9-13  | 34 | IOLBZ     | Ana. Out | Buffered analog output                             |

|--------|----|-----------|----------|----------------------------------------------------|

| P9-16  | 35 | IOLAZ     | Ana. Out | Buffered op-amp output                             |

| P9-15  | 36 | IOLAY     | Ana. In  | Buffered Analog input                              |

| P9-18  | 37 | IOLAX     | Ana. In  | Unbuffered Analog input                            |

| P9-17  | 38 | VREFOUT   | Ana. Out | Reference voltage                                  |

| AVDD   | 39 | BVDD      | Pwr/Gnd  | Bandgap VDD, 5 Volts                               |

| AGND   | 40 | BVSS      | Pwr/Gnd  | Bandgap VSS, 0 Volts                               |

| P8-20  | 41 | VMR       | Ana. Out | Signal ground, 2.5 Volts                           |

|        |    |           |          | (normally left floating)                           |

| P8-19  | 42 | OPAMP_VMR | Ana. In  | Signal ground, 2.5 Volts                           |

|        |    |           | -        | (usually loaded with 10nF to AVSS)                 |

| P8-18  | 43 | CEXT      |          | External VMR capacitor                             |

|        |    |           |          | (usually loaded with 10nF to AVSS)                 |

| P8-17  | 44 | IOD5Z     | Ana. Out | Buffered op-amp output                             |

| P8-16  | 45 | IOD5Y     | Ana. In  | Buffered Analog input                              |

| P8-15  | 46 | IOD5X     | Ana. In  | Unbuffered Analog input                            |

| P8-14  | 47 | IOD4Z     | Ana. Out | Buffered op-amp output                             |

| P8-13  | 48 | IOD4Y     | Ana. In  | Buffered Analog input                              |

| P8-12  | 49 | IOD4X     | Ana. In  | Unbuffered Analog input                            |

| DVDD   | 50 | ESD VDD   | Pwr/Gnd  | ESD Structures VDD, 5 Volts                        |

| DGND   | 51 | ESD VSS   | Pwr/Gnd  | ESD Structures VSS, 0 Volts                        |

| P8-9   | 52 | IOD3Z     | Ana. Out | Buffered op-amp output                             |

| P8-8   | 53 | IOD3Y     | Ana. In  | Buffered Analog input                              |

| P8-7   | 54 | IOD3X     | Ana. In  | Unbuffered Analog input                            |

| P8-6   | 55 | IOD2Z     | Ana. Out | Buffered Analog output                             |

| P8-5   | 56 | IOD2Y     | Ana. In  | Buffered Analog input                              |

| P8-4   | 57 | IOD2X     | Ana. In  | Unbuffered Analog input                            |

| P8-3   | 58 | IOD1Z     | Ana. Out | Buffered Analog output                             |

| P8-2   | 59 | IOD1Y     | Ana. In  | Buffered Analog input                              |

| P8-1   | 60 | IOD1X     | Ana. In  | Unbuffered Analog input                            |

| P7-20  | 61 | IORAX     | Ana. In  | Unbuffered Analog input                            |

| P7-19  | 62 | IORAY     | Ana. In  | Buffered Analog input                              |

| P7-18  | 63 | IORAZ     | Ana. Out | Buffered Analog output                             |

| P7-17  | 64 | IORBZ     | Ana. Out | Buffered Analog output                             |

| P7-16  | 65 | IORBY     | Ana. In  | Buffered Analog input                              |

| P7-15  | 66 | IORBX     | Ana. In  | Unbuffered Analog input                            |

| DVDD   | 67 | CFG VDD   | Pwr/Gnd  | Configuration (Digital) VDD ,5 Volts               |

| AGND   | 68 | SVSS      | Pwr/Gnd  | Substrate VSS, 0 Volts                             |

| AVDD   | 69 | SVDD      | Pwr/Gnd  | Substrate VDD, 5 Volts                             |

| P10-2  | 70 | CLOCK     | Dig. In  | System master clock. Used by clock generator which |

| 1 10 2 |    | 0L00IX    | Dig. III | feeds all switch capacitor analog circuitry.       |

| P7-10  | 71 | IORCX     | Ana. In  | Unbuffered Analog input                            |

| P7-9   | 72 | IORCY     | Ana. In  | Buffered Analog Input                              |

| P7-8   | 73 | IORCZ     | Ana. Out | Buffered Analog output                             |

| P7-7   | 74 | IORDY2    | Ana. In  | Uncommitted op-amp input                           |

| P7-6   | 75 | IORDZ2    | Ana. Out | Uncommitted op-amp output                          |

| DGND   | 76 | CFG VSS   | Pwr/Gnd  | Configuration (Digital) VSS, 0 Volts               |

| P7-4   | 77 | IORDZ     | Ana. Out | Buffered Analog output                             |

| P7-3   | 78 | IORDY     | Ana. In  | Buffered Analog output                             |

| P7-2   | 79 | IORDX     | Ana. In  | Unbuffered Analog input                            |

| DGND   | 80 | POR       | Dig. In  | Power on Reset (normally tied to VSS)              |

|        | 00 |           | Lug. III |                                                    |

13

# Downloading to your Target System

Once your design progresses to the point where you are ready to start booting your own target system containing an AN10E40, the AN10DS40 is still ready to serve you. When driving the development board via its RS-232 port, shorting the J1 jumper instructs the microcontroller to route all configuration traffic to the P2 External Target Array interface, rather than to the on board FPAA. The design systems otherwise behaves as if it were talking to the on board FPAA. In this fashion, the AN10DS40 now serves as an intelligent download cable to your target system, translating ASCII Hex configuration data from RS-232 to binary compatible with the AN10E40's Boot From ROM port.

Please refer to the design system schematic in Appendix C for connection details.

# Advanced User Topics

# The Microcontroller's Memory Map

Before covering any unfamiliar landscape its good to have a map handy. Please refer back to these maps as the discussion of the firmware progresses. All addresses and address contents are shown in hex. The first table shows a high level view of the entire memory map, showing only major sections. Subsequent tables show more detail for each of these major sections.

| Mem. Type | Section Name                 | Addrs. | Description                                                                                              |

|-----------|------------------------------|--------|----------------------------------------------------------------------------------------------------------|

| RAM       | IO and RAM                   | 0000   | Configuration and Data registers for IO Ports and                                                        |

|           |                              | 023F   | RAM area for program execution                                                                           |

|           | Unimplemented                | 0240   | Unimplemented portion of the memory map.                                                                 |

|           |                              | 7FFF   |                                                                                                          |

| Flash     | FPAA Configuration Files     | 8000   | Four blocks of Flash. Each contains a unique non-<br>volatile configuration image for the AN10E40. Great |

|           |                              |        | for stand alone demonstrations of the AN10DS40                                                           |

|           |                              | 8DFF   | system.                                                                                                  |

|           | User Playground              | 8E00   | The user is free to experiment in this area of Flash.                                                    |

|           |                              | CFFF   |                                                                                                          |

|           | ABK                          | D000   | This area contains the Anadigm Boot Kernal (ABK).                                                        |

|           |                              |        | This is the program that allows AnadigmDesigner to                                                       |

|           |                              | FAFF   | talk to the AN10DS40 board.                                                                              |

| Protected | Protected ABK                | FB00   | This portion of Flash is protected from erasure. It                                                      |

| Flash     |                              | FDFF   | contains the bootloader portion of the ABK.                                                              |

| RAM, ROM  | Status, Control, Monitor ROM | FE00   | This final section contains status and control registers                                                 |

| and FLASH | and ISR Vectors              |        | for many of the micro's features. Also in this range is                                                  |

|           |                              |        | a small monitor program in ROM as well as vectors                                                        |

|           |                              | FFFF   | for each of the interrupt sources routines (ISRs).                                                       |

### High Level View - The Complete Memory Map

## IO and RAM

| Area Name                | Addrs. | Contents       | Description                                            |

|--------------------------|--------|----------------|--------------------------------------------------------|

| IO Registers             | 0000   |                | IO Data and Control registers, including: MPIO ports,  |

|                          | 003F   |                | SPI, SCI etc.                                          |

| Bootloader Variables     | 0040   | reserved       |                                                        |

|                          | 0041   | reserved       |                                                        |

|                          | 0042   | reserved       |                                                        |

|                          | 0043   | First Addr. Hi | First address of Flash to be erased or programmed      |

|                          | 0044   | First Addr. Lo |                                                        |

|                          | 0045   | Last Addr. Hi  | Last address +1 of Flash to be erased or programmed    |

|                          | 0046   | Last Addr. Lo  |                                                        |

| User Application and ABK | 0100   |                | User Application and ABK RAM space.                    |

|                          | 01DF   |                |                                                        |

| Bootloader Stack and RAM | 01E0   |                | The stack is initialized at 0200 and grows up to 01E0. |

| Execution Space          |        |                | The remainder of this space is used for RAM            |

|                          | 023F   |                | execution routines.                                    |

# FPAA Configuration Files

| Area Name            | Addrs. | Contents | Description                                           |

|----------------------|--------|----------|-------------------------------------------------------|

| Configuration File 1 | 8000   |          | This is the FPAA configuration image that gets loaded |

| _                    | 837F   |          | into the AN10E40 when pushbutton S1 is pressed.       |

| Configuration File 2 | 8380   |          | when pushbutton S2 is pressed.                        |

| _                    | 86FF   |          |                                                       |

| Configuration File 3 | 8700   |          | when pushbutton S3 is pressed.                        |

|                      | 8A7F   |          |                                                       |

| Configuration File 4 | 8A80   |          | when pushbutton S4 is pressed.                        |

| _                    | 8DFF   |          |                                                       |

# User Playground

| Area Name       | Addrs. | Contents | Description                                              |

|-----------------|--------|----------|----------------------------------------------------------|

| User Playground | 8E00   |          | This area is left available to the advanced user for the |

|                 |        |          | installation of custom software. A typical use might be  |

|                 |        |          | a program which uses the microcontroller's A-D           |

|                 |        |          | converter in conjunction with the FPAA to yield even     |

|                 | CFFF   |          | more powerful applications.                              |

# ABK

| Area Name              | Addrs. | Contents       | Description                                           |

|------------------------|--------|----------------|-------------------------------------------------------|

| General ABK Code       | D000   |                | The unprotected portion of the ABK resides in this    |

|                        |        |                | area. This portion of the ABK handles things like the |

|                        |        |                | SPI interface, configuration Flash programming and    |

|                        | FABF   |                | AN10E40 configuration.                                |

| Configuration Settings | FAC0   | reserved       |                                                       |

|                        | FAC1   | reserved       | MC68HC908GP32 specific parameters                     |

|                        | FAC2   | reserved       |                                                       |

|                        | FAC3   | Init_Baud      | Initial BAUD register value (default = 0x30)          |

|                        | FAC4   | Init_Config1   | Initial CONFIG1 register value (default = 0x01)       |

|                        | FAC5   | Init_Config2   | Initial CONFIG2 register value (default = 0x03)       |

|                        | FAC6   | First Addr. Hi | Initial First Address to be erased or programmed      |

|                        | FAC7   | First Addr. Lo | (default = 0x8000)                                    |

|                        | FAC8   | Last Addr. Hi  | Initial Last Address +1 to be erased or programmed    |

|                        | FAC9   | Last Addr. Lo  | (default = 0xFB00)                                    |

| Jump Table             | FACA   | JMP Hi/Lo      | "JMP" and Hi&Lo address bytes for the Timebase ISR    |

| •                      | FACD   | JMP Hi/Lo      | for ADC                                               |

|                        | FAD0   | JMP Hi/Lo      | for Keyboard                                          |

|                        | FAD3   | JMP Hi/Lo      | for SCI Transmit                                      |

|                        | FAD6   | JMP Hi/Lo      | for SCI Receive                                       |

|                        | FAD9   | JMP Hi/Lo      | for SCI Error                                         |

|                        | FADC   | JMP Hi/Lo      | for SPI Transmit                                      |

|                        | FADF   | JMP Hi/Lo      | for SPI Receive                                       |

|                        | FAE2   | JMP Hi/Lo      | for Timer2 Overflow                                   |

|                        | FAE5   | JMP Hi/Lo      | for Timer2 Channel 1                                  |

|                        | FAE8   | JMP Hi/Lo      | for Timer2 Channel 0                                  |

|                        | FAEB   | JMP Hi/Lo      | for Timer1 Overflow                                   |

|                        | FAEE   | JMP Hi/Lo      | for Timer1 Channel 1                                  |

|                        | FAF1   | JMP Hi/Lo      | for Timer1 Channel 0                                  |

|                        | FAF4   | JMP Hi/Lo      | for PLL                                               |

|                        | FAF7   | JMP Hi/Lo      | for IRQ                                               |

|                        | FAFA   | JMP Hi/Lo      | for SWI                                               |

|                        | FAFD   | JMP Hi/Lo      | for RESET of the ABK                                  |

| Area Name     | Addrs. | Contents | Description                                                                                                                                                                                                                                                                                                          |

|---------------|--------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Protected ABK | FB00   |          | This area of Flash is protected from erasure. It contains the bootloader portion of the ABK. This portion of the ABK is the first to run out of a reset condition. It checks the state of the IRQ line, and if low drops into a terminal hosting mode which allows the erasure and reprogramming of the remainder of |

|               | FDFF   |          | Flash.                                                                                                                                                                                                                                                                                                               |

# Protected ABK

# Status, Control, Monitor ROM and ISR Vectors

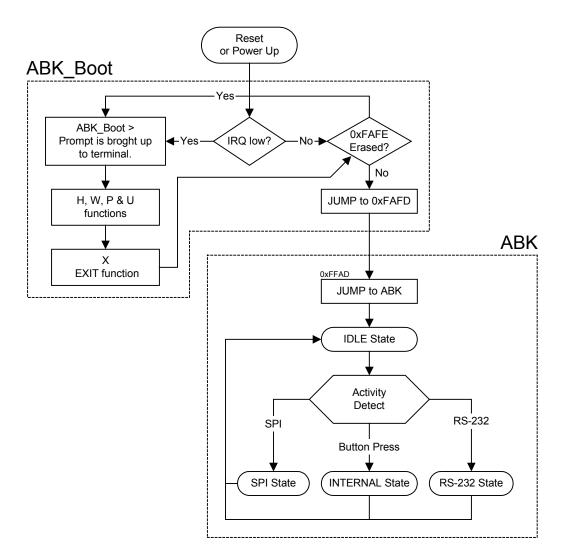

| Mem. Type and Area Name   | Addrs. | Contents | Description                                              |

|---------------------------|--------|----------|----------------------------------------------------------|

| RAM - Status and Control  | FE00   |          | Status and Control registers for things like the SIM,    |

|                           | FE0C   |          | Flash, Interrupt Controller and Breakpoint unit.         |

| ROM - Monitor ROM         | FE20   |          | Monitor ROM                                              |

|                           | FE52   |          |                                                          |

| RAM - Flash Block Protect | FE7F   |          | Flash Block Protect Register - This is the register that |