# Électronique Analogique Intégrée

Traitement et Propagation des Signaux Physiques

# Cours

AST1, AST2 et CC1— 2006-2007

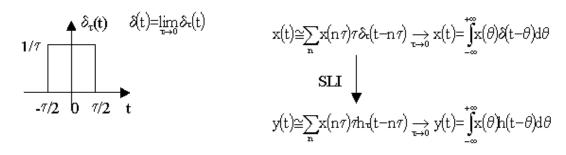

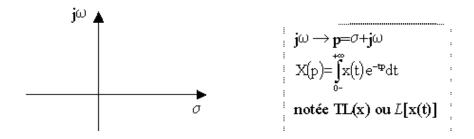

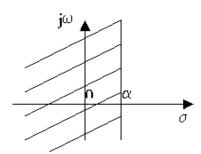

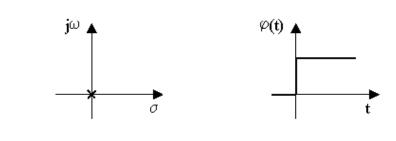

Patricia Desgreys Patrick Loumeau Jean-François Naviner Van Tam Nguyen Hervé Petit Jean Provost

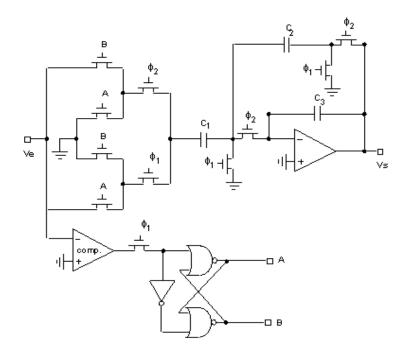

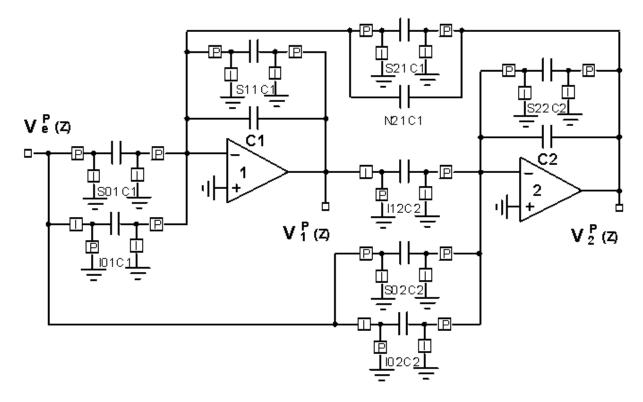

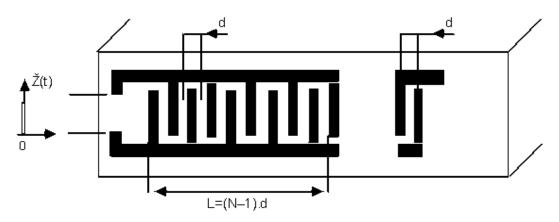

Direction de la Formation Département Communications et Électronique École Nationale Supérieure des Télécommunications

# Table des matières

| In | formations pratiques                                                      | 5   |

|----|---------------------------------------------------------------------------|-----|

| 1  | Introduction à l'électronique analogique intégrée                         | 7   |

| 2  | Du Silicium aux transistors                                               | 17  |

| 3  | Amplification                                                             | 41  |

| 4  | Outils de théorie du signal :<br>Transformée de Laplace, Transformée en Z | 65  |

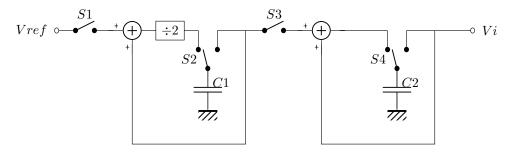

| 5  | Technique des Capacités Commutées                                         | 91  |

| 6  | Filtrage analogique                                                       | 103 |

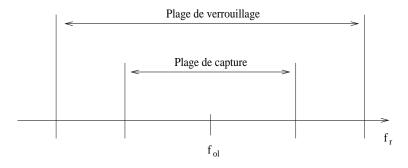

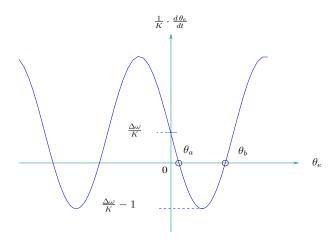

| 7  | Boucle à verrouillage de phase                                            | 121 |

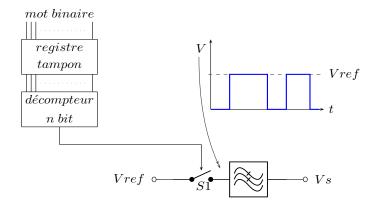

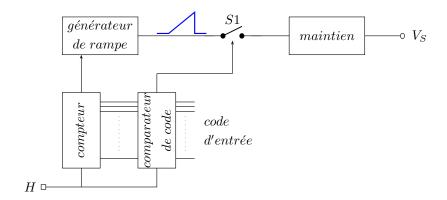

| 8  | La conversion analogique - numérique                                      | 133 |

| 9  | Du système au composant                                                   | 151 |

# Informations pratiques

Les informations actualisées relatives au module EAI sont disponibles sur l'intranet de l'ENST à l'adresse :

www.comelec.enst.fr/tpsp/eai/.

Les transparents de la plupart des cours sont disponibles sur l'intranet de l'ENST Paris à l'adresse :

www.comelec.enst.fr/tpsp/eai/transparents/.

## Remarque

- Le chapitre 2 « Du silicium aux transistors » est traité dans le cadre du module EAI pour les AST2 et dans le cadre du module SC (Semiconducteurs) pour les CC1 et AST1.

- Le chapitre 4 « Outils de théorie du signal : transformée de Laplace, transformée en Z » est l'objet de leçons uniquement pour les CC1 et AST1 dans la mesure où son contenu est supposé déjà acquis par les AST2.

- La section 8.4 « La conversion numérique analogique » du chapitre 8 « La conversion analogique - numérique » n'est pas au programme du module EAI.

- Le chapitre 9 « Du système au composant » est uniquement au programme pour les CC1 et AST1.

## Correspondances

Le tableau ci-dessous résume les correspondances de numérotation des chapitres de ce polycopié avec les leçons dispensées.

| Chapitre | Intitulé                                          | Leçon       | Leçon  |

|----------|---------------------------------------------------|-------------|--------|

|          |                                                   | CC & AST 1A | AST 2A |

| 1        | Introduction à l'électronique analogique intégrée | 1           | 1      |

| 2        | Du silicium aux transistors                       |             | 2      |

| 3        | Amplification                                     | 2           | 3      |

| 4        | Outils de théorie du signal :                     | 3 & 4       |        |

|          | Transformée de Laplace, Transformée en Z          |             |        |

| 5        | Technique des Capacités Commutées                 | 5           | 4      |

| 6        | Filtrage analogique                               | 6           | 5      |

| 7        | Boucle à verrouillage de phase                    | 7           | 6      |

| 8        | La conversion analogique - numérique              | 8           | 7      |

| 9        | Du système au composant                           | 9           |        |

Tab. 1 – Correspondances de numérotation des chapitres et leçons

# Chapitre 1

# Introduction à l'électronique analogique intégrée

#### 1.1 Introduction

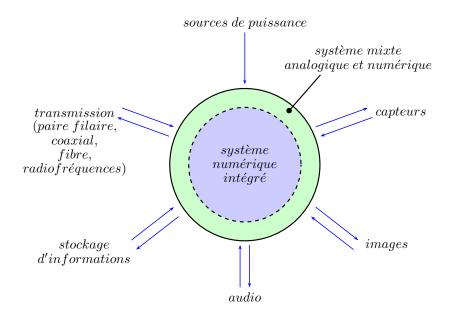

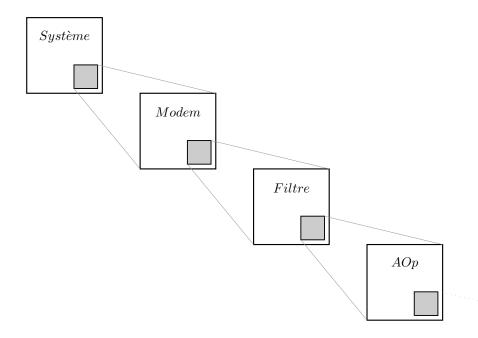

L'électronique intégrée ou microélectronique est habituellement divisée en de grands domaines partiellement recouvrants et aux limites floues : la fourniture de puissance, la transduction (acquisition ou restitution d'une information extérieure non " électronique ") et le traitement du signal qu'il soit numérique ou analogique. De plus en plus, ces divers aspects de l'électronique sont pris en compte conjointement au sein de systèmes toujours davantage intégrés jusqu'à l'obtention d'une solution monolithique.

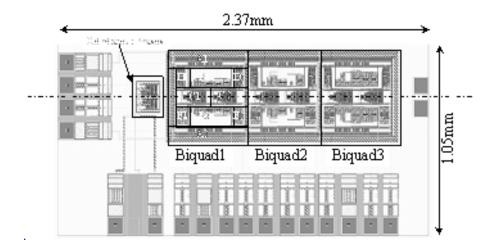

Dans ce chapitre, nous nous limiterons à évoquer l'électronique intégrée pour le traitement du signal sous forme analogique ou mixte. La première partie présente le contexte économique général. La seconde partie aborde les considérations technologiques propres à la microélectronique analogique ou mixte. La troisième partie présente succinctement la méthode de conception de systèmes intégrés analogiques ou mixtes. Enfin, un exemple de circuit conclut ce chapitre.

## 1.2 Contexte de l'électronique analogique intégrée

#### 1.2.1 Contexte économique

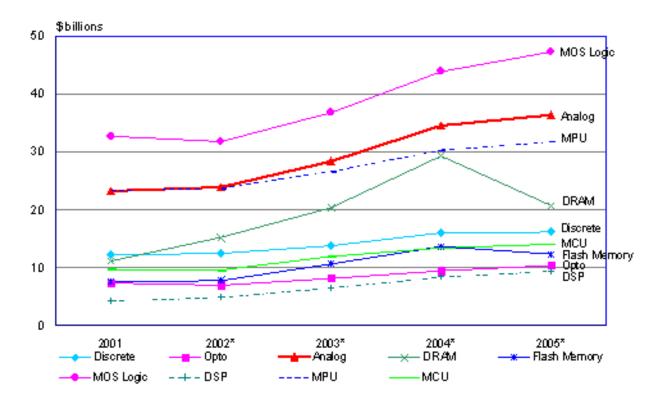

Les statistiques économiques de la microélectronique montrent que la part relative des circuits analogiques au sein de la production mondiale est désormais stable depuis quelques années. Les composants analogiques représentent environ 17% du marché total des semiconducteurs. Le volume de production des circuits intégrés analogiques est en constante augmentation : les estimations (données 2003) indiquent une croissance de 17% pour les composants analogiques en 2003 et 19% en 2004. Pour les mêmes années, le marché total des semi-conducteurs devrait croître de 15% et 12% respectivement. Au sein du marché des composants analogiques, le marché des composants radio-fréquences évolue plus rapidement que celui des composants basse-fréquence. Ceci s'explique notamment par la prééminence actuelle du secteur des télécommunications et par la pénétration croissante de l'électronique dans l'automobile. La Figure 1 illustre la prévision de l'évolution du marché pour les principaux types de composants.

En fait, aujourd'hui, de nombreux circuits intègrent à la fois des parties numériques et des parties analogiques, constituant des systèmes mixtes. L'importance des systèmes mixtes est croissante. Du fait de l'évolution technologique, le traitement analogique ne constitue dans bien des cas qu'une composante de systèmes plus complexes. On parle alors de systèmes sur puce (systems on chip-SoC).

Les circuits analogiques sont classés en trois catégories :

- les circuits standards : amplificateurs, comparateurs, convertisseurs...

- les circuits dédiés à une application : automobile, télécommunications, télévision, radiofréquences...

- les autres : filtres, codec, circuits pour les modems...

Les deux dernières catégories sont les plus vendues. Les applications en télécommunication ont une croissance particulièrement forte.

#### 1.2.2 Rôle de l'électronique analogique intégrée

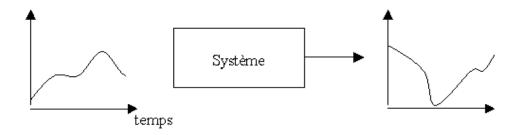

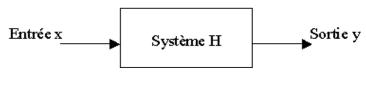

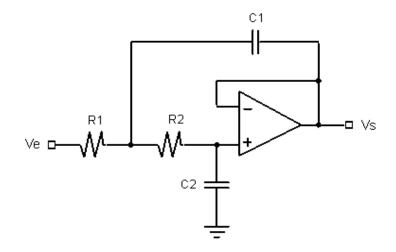

Les circuits analogiques jouent un rôle important dans tous les systèmes pour lesquels une communication directe avec le monde " réel ", par essence analogique, est nécessaire. Les systèmes analogiques sont irremplaçables pour cette interface avec les systèmes VLSI numériques (Fig. 1.1). Les fonctions nécessaires sont principalement la conversion analogique-numérique et numérique-analogique, l'amplification, le filtrage et la transduction.

Les systèmes de télécommunications font en particulier appel à de nombreuses réalisations

Fig. 1.1 – Evolution du marché des semi-conducteurs (Source : SIA [4])

analogiques chaque fois que le passage entre le monde extérieur analogique et une représentation numérique de l'information est nécessaire.

Le traitement analogique du signal est également préférable à un traitement numérique pour de nombreuses applications pour lesquelles une faible précision est nécessaire (certains réseaux de neurones, par exemple).

Le tableau ci-dessous présente les caractéristiques exigées d'un système de traitement du signal pour quelques exemples d'application.

| TAB. 1.1 – . Exemples de performance           | TAB. 1.1 – . Exemples de performances de systèmes analogiques |              |  |

|------------------------------------------------|---------------------------------------------------------------|--------------|--|

| radiofréquences                                | 100MHz à 10GHz                                                | 8 à 10 bits  |  |

| stockage magnétique                            | 100 à 500MHz                                                  | 6 à 8 bits   |  |

| TV numérique multi-standard                    | 20MHz                                                         | 8 à 10 bits  |  |

| TV haute définition                            | 50 à 75MHz                                                    | 10 bits      |  |

| traitement des fréquences intermédiaires radio | 1 à 50MHz                                                     | 8 à 10 bits  |  |

| audio                                          | 50Hz à 40KHz                                                  | 16 bits      |  |

| métrologie                                     | < 1Hz à 1KHz                                                  | 16 à 24 bits |  |

TAB. 1.1 – : Exemples de performances de systèmes analogiques

#### 1.2.3 Exemples de composants

Voici quelques exemples de composants analogiques utilisés en électronique analogique intégrée :

- 1. Amplificateur opérationnel,

- 2. Amplificateurs d'instrumentation,

- 3. Références de tension,

- 4. Amplificateurs échantillonneurs-bloqueurs,

Fig. 1.2 – Rôle des circuits analogiques dans les télécommunications

- 5. Convertisseurs A-N et N-A,

- 6. Multiplexeurs analogiques,

- 7. Boucles à verrouillage de phase,

- 8. Comparateurs,

- 9. Amplificateurs de puissance.

## 1.3 Défis techniques

Comme nous l'avons expliqué précédemment, l'intégration de fonctions de traitement du signal analogique est indispensable pour pouvoir mettre en oeuvre des systèmes interagissant avec l'environnement. Ceci concerne par exemple quasiment tous les systèmes de communications. Les attentes évoluent : des bandes passantes toujours plus larges sont nécessaires, les bandes de fréquences utilisées également du fait de l'encombrement croissant du spectre. Dans le même temps, les informations à émettre, à recevoir, à traiter sont plus hétérogènes et requièrent des puissances de calcul toujours accrues. Pour qu'existe un marché significatif, permettant entre autre à l'industrie électronique de poursuivre son développement, le coût final des produits doit rester abordable et en tout cas en rapport avec le service fourni et l'innovation introduite. Afin de répondre à ces exigences, de nouvelles technologies sont en permanence mises au point. Elles sont presque toujours optimisées en premier lieu pour l'intégration de l'électronique numérique. Cependant, l'intégration de systèmes monopuces confère aujourd'hui à l'intégration de fonctions analogiques ou radiofréquences une part croissante dans l'évolution technologique. Pour répondre aux attentes exprimées ci-dessus, les chercheurs et développeurs en électronique analogique doivent relever de nombreux défis dont les principaux sont exposés dans ce qui suit.

#### 1.3.1 Critères de performances

Les critères sont variés. Leur importance relative varie d'une application à une autre. Citons les plus courants : la largeur de bande de fréquences, la consommation d'énergie, la surface de circuit nécessaire à la mise en oeuvre, la linéarité, le rapport signal sur bruit, la dynamique, la fiabilité, les potentialités de programmation ou de reconfiguration. IL est important de noter que ces différents critères sont liés de façon complexe. Gagner sur un critère peut induire de plus grandes difficultés à satisfaire les exigences sur un autre.

#### 1.3.2 Vitesse, bandes de fréquences

Les progrès réalisés en communications numériques ont permis en particulier d'augmenter le débit de transmission pour une même largeur de bande. Cette augmentation n'est pas suffisante pour couvrir avec des bandes de quelques centaines de kHz les besoins liés à de nouveaux usages tels que la visualisation de vidéo (en différentes qualités) sur des terminaux mobiles (réseaux cellulaires ou locaux). L'accroissement des largeurs de bande requiert des composants électroniques adaptés, amplificateurs, filtres, convertisseurs, etc. tout en maintenant les exigences en rapport signal sur bruit, en consommation, en linéarité... Pour y parvenir, la seule innovation technologique n'est pas suffisante. L'innovation en techniques de traitement du signal, en circuiterie et en architecture est indispensable.

#### 1.3.3 Consommation d'énergie

Une fois les spécifications d'un système établies à partir des données de l'application, de l'usage particulier, et des normes considérées, des performances minimales et nominales pour chaque sous-partie du système peuvent être déterminées après choix d'un partitionnement matériel-logiciel puis d'un partitionnement analogique-numérique (voir 9). Le respect de ces performances par le système construit est indispensable pour garantir la fonctionnalité au regard de l'application envisagée. D'autres caractéristiques telles que la consommation n'interviennent pas directement dans la fonctionnalité mais ont un impact direct sur le coût du produit et donc sur sa compétitivité. La consommation peut aussi avoir un impact sur l'encombrement ou l'autonomie du produit et donc sur son ergonomie et sa praticité. Moins consommer d'énergie signifie soit une meilleure autonomie avec un même type de batterie, soit des batteries moins encombrantes ou moins onéreuses pour une même autonomie. Moins consommer d'énergie répond aussi à une préoccupation croissante de nature environnementale et écologique. Là encore, l'innovation technologique contribue à cet objectif à condition d'y associer l'innovation en circuit, en architecture et en gestion de la consommation. Ce dernier point (power management, power-aware system) est devenu une préoccupation systématique au sein de systèmes complexes ([ref]). L'écart entre les prévisions technologiques ([ref]) et les prévisions de performances de systèmes futurs montrent que l'innovation technologique ne pourra suffire à elle seule à répondre aux attentes.

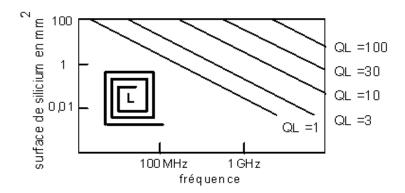

#### 1.3.4 Surface d'un circuit, volume d'un système

Le couple (technologie, surface de puce) joue un rôle très important dans le coût final d'un produit. La réduction de la surface de circuit pour la mise en oeuvre d'une fonction peut cependant engendrer d'autres difficultés comme une énergie dissipée par unité de surface accrue. Des moyens d'évacuation de la chaleur doivent alors être mis en oeuvre. Le choix d'une filière technologique (CMOS, BiCMOS, SiGe, SOI, AsGa, etc.) puis d'une génération technologique influe sur la faisabilité du système, sur la surface de puce nécessaire et donc sur le coût final. Au sein d'une même filière, le CMOS par exemple, il faut encore déterminer si des "options" technologiques sont souhaitables: transistors à faible tension de seuil, matériau fortement résistif, oxyde mince entre couches métalliques pour implantation de capacités, etc. Pour chaque projet, ce choix doit être établi en fonction de la prévision de surface, du coût surfacique de la technologie, du surcoût des options, etc. mais aussi du savoir-faire des concepteurs dans la technologie considérée, de la disponibilité de plusieurs sources de fonderie, de la possibilité de réutiliser pour d'autres projet le travail effectué... Pour une filière donnée, la technologie la plus avancée ne constitue pas toujours le meilleur choix : là encore, une estimation de surface pour le système complet est nécessaire. Les fonctions numériques bénéficient pleinement de l'avancée technologique en terme de densité et de vitesse. Il n'en va pas de même pour les blocs analogiques dont la surface ne diminue que très lentement en fonction de l'évolution technologique. En revanche, le coût du  $mm^2$  de circuit croît très fortement d'une génération technologique à une autre.

#### 1.3.5 Intégration de systèmes monopuces

L'intégration de systèmes monopuces induit divers défis techniques dont certains déjà cités précédemment. Nous pouvons ajouté à ceux déjà cités précédemment, la nécessaire maîtrise des couplages et interférences sur la puce. Certains composants sont sources de bruit, d'autres composants ou matériaux le transportent et d'autres enfin sont particulièrement sensibles. En particulier, les circuits analogiques sensibles doivent être isolés le plus possibles des circuits numériques, sources de bruit dû aux commutations.

#### 1.3.6 Outils d'aide à la conception

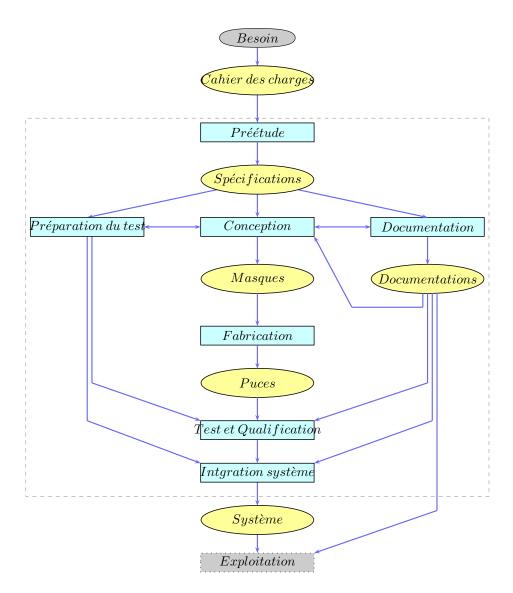

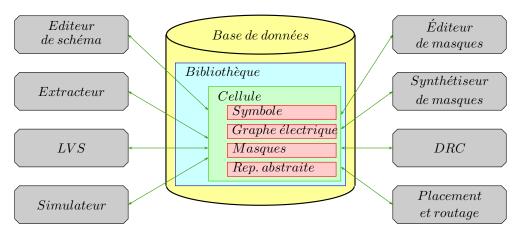

La maîtrise des coûts impose l'emploi d'outils d'aide à la conception afin d'améliorer et de fiabiliser la production. IL s'agit :

- d'outils de synthèse pour affiner une représentation de tout ou partie d'un système jusqu'à la création des masques (représentation bidimensionnelle des différentes couches conductrices et semi-conductrices constituant la structure physique d'un circuit);

- d'outils d'analyse et de vérification pour s'assurer que les performances atteintes sont conformes aux spécifications.

Ces outils sont traités plus en détail au Chapitre 9. Il est important de noter que la conception de circuits analogiques ou mixtes est encore en grande partie non automatisée requérant ainsi le savoir-faire de concepteurs spécialisés.

#### 1.4 Exemples de systèmes mixtes

Dans ce qui suit, nous traitons deux exemples de systèmes mixtes appliqués à des domaines distincts. Nous verrons que bien que très différents, ces systèmes ont de nombreux objectifs communs en terme de conception.

#### 1.4.1 Prothèse auditive, implant cochléaire

#### Définition

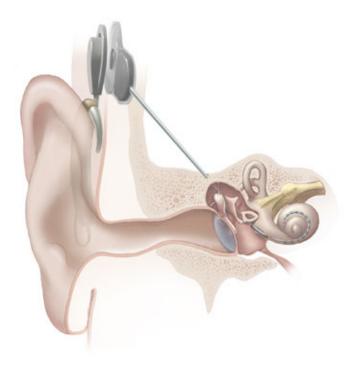

Un implant cochléaire est un dispositif électronique conçu pour induire de sensations auditives utiles au patient malentendant par une stimulation électrique des nerfs à l'intérieur de l'oreille interne. Il est important de noter qu'un système d'implant cochléaire est très différent d'un dispositif d'aide auditive. Ce dernier capte, amplifie et restitue le son. L'implant cochléaire a pour objet de compenser des défaillances partielles ou complètes de parties de l'oreille interne. Lorsque l'oreille interne fonctionne normalement, elle convertit le son en stimuli électriques transmis au cerveau. L'implant cochléaire réalise la même fonction même s'il ne fournit pas à l'utilisateur exactement la même sensation. Ce système permet la communication sans toutefois assurer une restitution sonore fidèle.

#### Description du système

Il existe de nombreux types de prothèses auditives, nous considérons ici un exemple particulier : nous allons analyser la composition de ce système puis relever les caractéristiques représentant des défis techniques.

La Fig. 1.3 représente un système complet de prothèse auditive. Ce système comprend :

- un microphone pour capter le signal acoustique;

- un module de traitement du signal analogique et numérique associé à une chaîne d'émission;

- un module de réception et de stimulation;

un jeu d'électrodes implantées dans l'oreille interne, relié au module de stimulation par une liaison filaire.

Fig. 1.3 – Système de prothèse auditive à implant cochléaire (source : NIDCD [3])

#### Particularités du système

Une partie du système est invasive, c'est à dire qu'elle est implantée à l'intérieur du corps humain. Cette partie (les électrodes et le module connecté) doit donc :

- ne pas entraîner de rejet;

- ne pas provoquer de dommage lors de la mise en place ou lors du fonctionnement;

- ne pas entraîner de nuisance pour l'utilisateur;

- disposer d'une autonomie importante;

- être adaptable aux spécificités de chaque patient;

- nécessiter une intervention chirurgicale la plus légère possible.

#### Ces particularités requièrent donc :

- une très grande fiabilité;

- une très faible consommation et éventuellement la mise en oeuvre de récupération d'énergie;

- une miniaturisation poussée;

- des possibilités de réglages et de contrôle.

La partie non implantée doit également :

- être peu encombrante et légère (tenir dans une poche);

- disposer d'une autonomie suffisante;

- être fiable (en particulier, ne pas transmettre à l'implant des signaux perturbants).

#### 1.4.2 Chaîne d'émission-réception radio

#### **Définition**

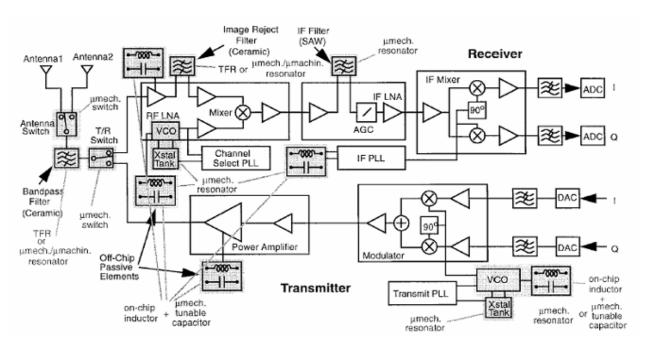

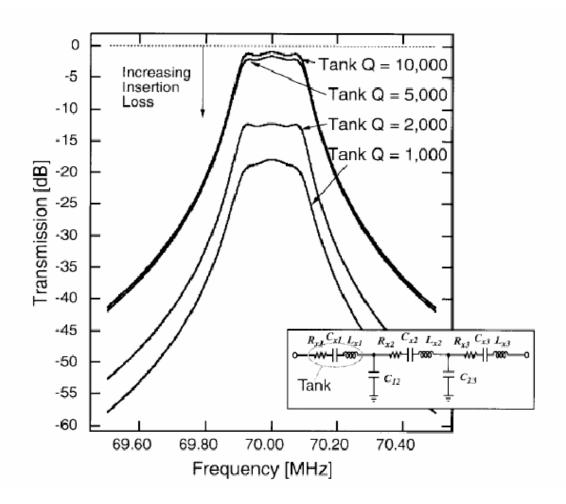

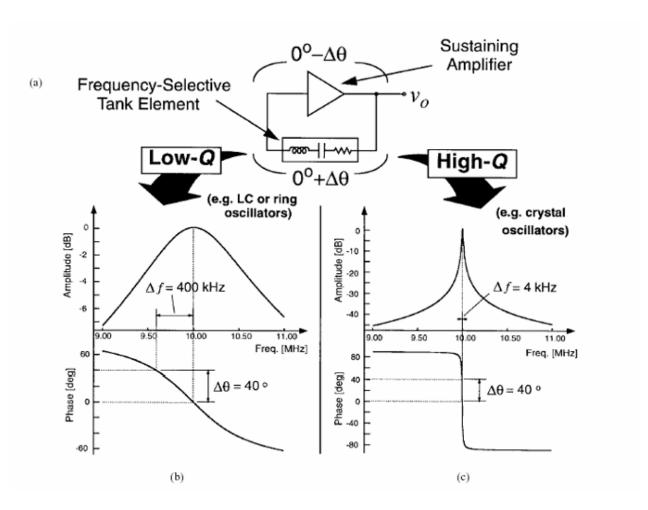

La chaîne d'émission-réception radio est étudiée en détail dans le cadre de la brique ISER (Cycle Optionnel Unifié). Nous nous contentons ici d'une description très générale. La chaîne

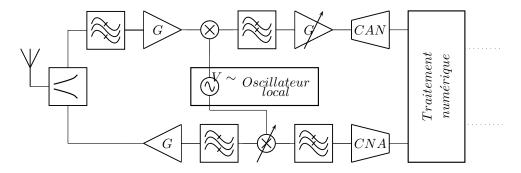

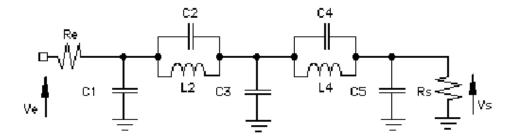

d'émission-réception radio est utilisée pour de très nombreuses applications aux contraintes très différentes. Nous nous contentons ici d'évoquer son application en communications cellulaires et plus précisément pour un terminal mobile. La chaîne d'émission réception radio (encore appelé frontal radiofréquences) a pour objet la transmission de signaux radiofréquences entre une station de base et le terminal mobile qui la contient. Elle réalise notamment les fonctions d'amplification, filtrage, translation en fréquences et conversion analogique-numérique ou numérique-analogique. Le frontal RF est une sous partie de l'ensemble complexe que constitue le terminal.

#### Description du système

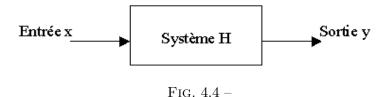

Un schéma simplifié d'émetteur-récepteur est représenté sur la Fig. 1.4.

Fig. 1.4 – Schéma simplifié d'un frontal radiofréquence)

Le système contient une chaîne d'émission (partie inférieure du schéma) et une chaîne de réception (partie supérieure du schéma). Ces deux chaînes se rejoignent avant l'antenne via un composant radiofréquences, appelé duplexeur à pour objet la séparation des signaux émis, de forte puissance, et des signaux reçus, de très faible puissance.

La voie de réception contient des filtres, des amplificateurs dont certains à gain variable, des mélangeurs (translatant le signal à des fréquences plus basses et finalement au moins un convertisseur analogique-numérique. Le signal ainsi numérisé est ensuite démodulé, décodé puis exploité pour l'application voulue.

A partir du signal à transmettre encore représenté sous forme numérique, la voie d'émission contient au moins un convertisseur numérique-analogique, des filtres, des mélangeurs et finalement un amplificateur de puissance.

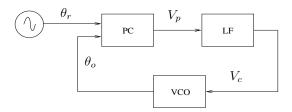

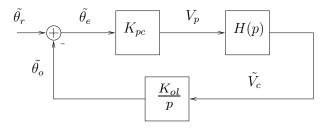

Des fréquences doivent être générées et contrôlées en interne pour le traitement correct des signaux. Des oscillateurs et des boucles à verrouillage de phase sont alors nécessaires.

#### Particularités du système

Dans le cas d'une chaîne d'émission-réception radio intégrée dans un terminal mobile, le système doit :

- ne pas entraı̂ner de nuisance évidente pour l'utilisateur ou son entourage;

- disposer d'une autonomie importante;

- être adaptable aux spécificités de chaque utilisateur;

- disposer d'une fiabilité élevée;

- avoir une très faible consommation et éventuellement mettre en oeuvre la récupération d'énergie;

- offrir une miniaturisation poussée et un faible poids;

- proposer des possibilités de programmation (customisation).

Ces caractéristiques influent sur l'ensemble des domaines de définition du système et en particulier sur la conception matériel/logiciel d'un tel système.

# 1.5 Bibliographie

# Bibliographie

- [1] MXM. www.mxmlab.com/fr/.

- [2] Australian Academy of Science. www.science.org.au/.

- [3] National Institute on Deafness and National Institutes of Health Other Communication Disorders. www.nidcd.nih.gov/health/.

- [4] W.J. Sanders. S.i.a. fall 2002 forecast, 2002. www.sia-online.org/.

# Chapitre 2

# Du Silicium aux transistors

#### 2.1 Introduction

#### 2.1.1 Historique

Le transistor MOS est un élément décisif dans l'évolution technologique de l'électronique. Celle ci permet la réalisation de circuits de traitement d'informations de très grandes performances et de très grande diffusion. Le moteur de cette évolution est la diminution des dimensions du transistor. Nous verrons comment cette diminution géométrique entraı̂ne une vitesse et une puissance de traitement plus grandes pour un coût, au sens général, plus faible.

La technologie (mot qui désigne ici l'ensemble des procédés matériels aboutissant à la fabrication de circuits intégrés) CMOS sur Silicium domine très largement l'industrie de l'électronique. Pourtant le premier transistor (contraction de l'anglais "transfer resistor") construit en 1947 aux Laboratoires Bell Telephone (aux États Unis) par Bardeen, Brattain et Shockley, fut un transistor bipolaire à pointes. Le premier transistor MOS ne fut construit qu'en 1961, au même endroit par Kahng et Atalla, bien que la première publication scientifique décrivant son principe de fonctionnement soit le fait de Lilienfeld en 1928.

Kilby de Texas Instruments en 1958 et Noyce de Fairchild Camera and Instrument en 1959 élaborèrent les premiers circuits intégrés bipolaires. Notons enfin que 2 ingénieurs de Fairchild, Moore et Noyce, fondèrent Intel en 1968 pour y développer les premiers circuits intégres MOS.

#### 2.1.2 Organisation de la leçon

Nous allons répondre aux questions suivantes :

- Comment fonctionne un circuit élémentaire à un transistor?

- Quelle fonction électrique doit réaliser un transistor?

- Quel phénomène physique utiliser pour celà?

- Comment construire un transistor?

- Comment modéliser son fonctionnement?

#### 2.2 Circuit élémentaire

Les systèmes de traitement de l'information utilisent, souvent de manière cachée mais quasi exclusivement, des transistors. De la même façon, l'information est portée par la variation d'un signal électrique. Ce signal peut être un courant, une tension, une quantité de charge, un champ électrique et/ou magnétique... La variable porteuse d'information peut être l'amplitude, la fréquence, ou la phase... Afin de simplifier l'exposé, nous supposerons que l'information est portée par l'amplitude de la tension du signal électrique.

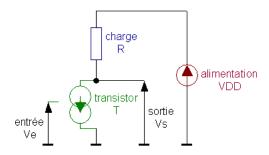

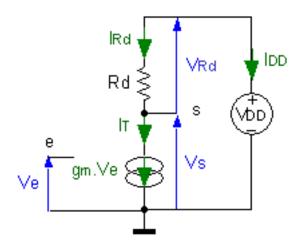

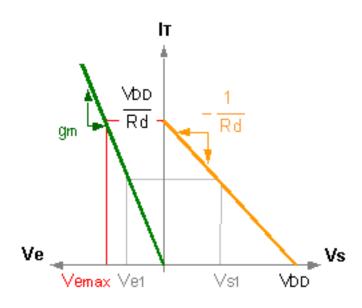

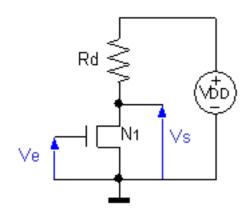

Le schéma de la figure 2.1 représente le circuit électronique permettant de réaliser la fonction élémentaire inversion/amplification.

Fig. 2.1 – Circuit élémentaire inverseur

Il est constitué de :

- une alimentation stabilisée, qui délivre une tension continue  $V_{DD}$ , quel que soit le courant sortant  $I_{DD}$  (source de tension constante idéale),

- une résistance de charge R, aux bornes de laquelle le courant qui la traverse  $I_R$ , engendre une tension  $V_R$  (loi d'Ohm) :  $V_R = R \cdot I_R$ ,

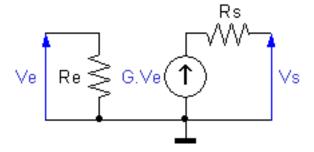

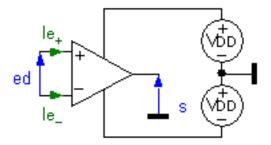

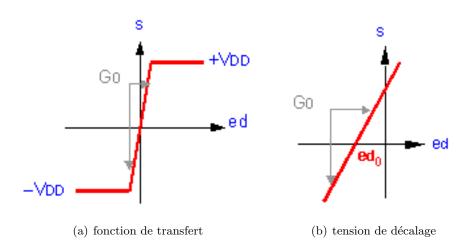

- un transistor T, dont le modèle est un quadripôle linéaire constitué de :

- dipôle de sortie : une source de courant dépendante linéairement de la tension d'entrée :  $I_T = G_m \cdot V_e$ ,

- dipôle d'entrée : un prélèvement de la tension d'entrée  $V_e$ .

Ce type de quadripôle est appelé une transconductance idéale.

Analysons le fonctionnement de ce circuit :

- en utilisant la loi des mailles, puis la loi d'Ohm, nous pouvons écrire :  $V_{DD}=V_R+V_s=R\cdot I_R+V_s$

- les seuls éléments connectés sur le nœud de sortie sont la charge R et le dipôle de sortie du transistor T. Ainsi, (loi des nœuds) nous pouvons écrire :  $I_{DD} = I_R = I_T$

- utilisons la transconductance idéale  $G_m$  du transistor :  $V_{DD} = R \cdot G_m \cdot V_e + V_s$

- nous obtenons la caractéristique de transfert  $V_s = f(V_e)$  du circuit :

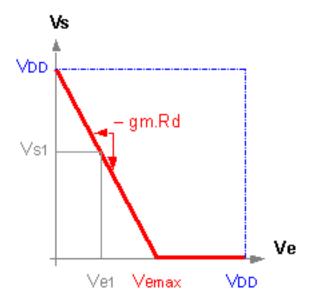

$$V_s = V_{DD} - R \cdot G_m \cdot V_e$$

Ce circuit est utilisé en électronique analogique pour réaliser, dans certaines conditions, la fonction amplification, dont le principal paramètre est le gain en tension :

$$G_v = \frac{\delta V_s}{\delta V_e} = -G_m \cdot R$$

De même il est utilisé en électronique numérique pour réaliser la fonction inversion logique. Dans ce type de traitement l'information est portée par les deux états extrêmes de l'amplitude de tension :

$$\begin{split} V_e = V_{DD} = \text{"1"} & \Rightarrow & I_T = I_{Tmax} \\ & \Rightarrow & V_R = R \cdot I_{Tmax} = -V_{DD} \\ & \Rightarrow & V_s = 0V = \text{"0"} \\ V_e = 0V = \text{"0"} & \Rightarrow & I_T = 0A \\ & \Rightarrow & V_R = 0V \\ & \Rightarrow & V_s = V_{DD} = \text{"1"} \end{split}$$

Poursuivons l'exemple de l'électronique numérique : le traitement de l'information consiste à faire commuter (dans certaines conditions qui spécifient la fonction logique réalisée) la tension du nœud de sortie de 0V à  $V_{DD}$  ou de  $V_{DD}$  à 0V. Le principal paramètre de performance du circuit logique est le temps mis pour passer d'un état logique à l'autre (vitesse).

Nous utilisons une modélisation simple du nœud de sortie où les seuls éléments passifs qui y sont connectés sont les capacités parasites des transistors et des connexions. Les équations de constitution du condensateur :

• condensateur idéal :  $Q = C \cdot V$ ,

• courant :  $I = \frac{dQ}{dt}$ ,

nous permettent d'obtenir :

• le temps de commutation :  $dt = C \cdot \frac{dV}{i}$

où:

- $dV = \pm VDD$  (suivant la transition "0"  $\mapsto$  "1" ou "1"  $\mapsto$  "0").

- C = capacité totale équivalente du nœud commutant,

- i = courant traversant le dipôle de sortie du transistor et chargeant C.

Il ne reste plus (!) qu'à identifier et caractériser i et C.

Dans ce chapitre nous allons donc voir comment le transistor MOS peut être réalisé à partir de matériaux semi-conducteurs tels que le Silicium.

Pour cela nous rappellerons quelques propriétés élémentaires des matériaux semi-conducteurs intrinsèques et dopés.

A l'aide de ces notions, nous décrirons la structure et le fonctionnement du transistor MOS de manière à disposer d'un modèle simple et quantifiable de l'intensité du courant de sortie et des capacités parasites du transistor MOS.

## 2.3 Rappels de physique simplifiée

#### 2.3.1 Notion de courant

Un courant électrique dans un matériau est un déplacement de charges libres. Il nécessite l'existence de :

- charges *libres*, c'est à dire ne participant pas aux liaisons de valence de la structure cristalline, donc libres de s'y déplacer,

- d'une force capable de les entraîner.

Pour simplifier, il existe deux types de courant : le courant de diffusion et celui de conduction.

#### Diffusion

La force de diffusion est due à un gradient de concentration (densité) de charges. Elle entraı̂ne les porteurs libres vers les régions de moindre concentration, créant ainsi un *courant de diffusion*. C'est celle qui est utilisée dans la jonction PN (voir plus loin) et dans l'effet bipolaire.

#### Conduction

Le champ électrique E engendre sur un porteur libre une force F:

$$F = q_c \cdot E$$

Compte tenu des frottements et des collisions avec le réseau cristallin, le porteur libre atteint rapidement une vitesse limite  $v_c$ :

$$v_c = \mu_c \cdot E$$

La densité du courant de conduction ainsi créé est J :

$$J = \sigma \cdot E = n_c \cdot q_c \cdot \mu_c \cdot E$$

Fig. 2.2 – Résistance d'un tube

- E est le champ électrique en  $V \cdot m^{-1}$ ,

- $\bullet$  F est la force d'entraı̂nement en N,

- $q_c$  est la charge du porteur libre en C (Coulomb),

- $\mu_c$  est sa mobilité dans ce matériau en  $m^2 \cdot V^{-1} \cdot s^{-1}$ ,

- $v_c$  est sa vitesse en  $m \cdot s^{-1}$ ,

- $\sigma$  est la conductivité en  $\Omega^{-1} \cdot m^{-1}$  ou en  $S \cdot m^{-1}$  de ce matériau pour ces charges libres,

- $n_c$  est la densité (concentration par unité de volume) des charges libres en  $m^{-3}$ ,

- J est la densité du courant de conduction en  $A \cdot m^{-2}$ ,

Ainsi nous pouvons modéliser un courant en connaissant :

- la technologie du matériau par :

- la mobilité de ses porteurs libres  $(\mu)$ ,

- leur densité dans la région active (n),

- la charge unitaire de ces porteurs  $(q_c)$ ,

- l'action appliquée : ici le champ électrique (E)

#### 2.3.2 Conducteur, semi-conducteur, dopages

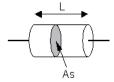

La résistance (en Ohms,  $\Omega$ ) d'un tube de longueur L, dont l'aire de la section est  $A_S$ , dans un matériau de conductivité  $\sigma$  est :

$$R = \frac{1}{\sigma} \cdot \frac{L}{A_S}$$

Nous allons expliquer succinctement le mode de conduction à la température ambiante dite normale et calculer la résistance d'un même tube de longueur L, d'aire de section  $A_S$  pour 4 types de matériau :

- un conducteur métallique,

- un semi-conducteur pur, le Silicium,

- du Silicium dopé N,

- du Silicium dopé P.

La charge de l'électron est  $q_e$  et la charge élémentaire est  $q=\mid q_e\mid$  (voir la valeur des paramètres communs dans le tableau 2.1.

| Dimensions               | Charges                                         | Température                          |  |

|--------------------------|-------------------------------------------------|--------------------------------------|--|

| $L = 10mm$ $A_S = 1mm^2$ | $q = q_{tr} = -q_e = 0,16 \ aC  (a = 10^{-18})$ | $T = 300K$ ou $\theta = 27^{\circ}C$ |  |

Tab. 2.1 – paramètres communs

#### Conducteur

Supposons que le matériau utilisé soit un métal de densité atomique  $N_m$  et dans lequel la mobilité des électrons est  $\mu_m$ . Supposons que chaque atome métallique fournisse un électron libre, ainsi la densité des électrons libres est  $n_m = N_m$  (voir le tableau 2.2).

| En résumé, pour un métal conducteur $(T = 300K)$                  |                                                                                |  |

|-------------------------------------------------------------------|--------------------------------------------------------------------------------|--|

| un électron libre par atome métallique : $n_m = N_m$              |                                                                                |  |

| Technologie                                                       | Résistance                                                                     |  |

| $N_m = 50 \cdot 10^{27} m^{-3}$ $\mu_m = 0, 15 m^2 V^{-1} s^{-1}$ | $R = \frac{1}{q \cdot n_m \cdot \mu_m} \cdot \frac{L}{A_S} \approx 8\mu\Omega$ |  |

Tab. 2.2 – paramètres du conducteur

#### Semi-conducteur pur

Le Silicium (Si) à l'état solide est un *semi-conducteur*, il forme un cristal de structure tétraédrique. Il appartient à la colonne IV de la classification périodique des éléments. Chaque atome Si est ainsi relié à ses 4 plus proches voisins par l'intermédiaire des 4 électrons de sa couche périphérique.

Un semi-conducteur est isolant au froid absolu (T = 0K) c'est à dire qu'aucun électron n'y est libre. À la température normale : T = 300K,  $\theta = 27^{\circ}C$  l'énergie fournie est telle que certains des électrons périphériques sont libres laissant autant d'atomes ionisés  $Si^{+}$ . À son tour l'ion  $Si^{+}$  peut capter l'électron d'un atome Si voisin. Le manque d'électron (l'ion  $Si^{+}$ ) peut ainsi se déplacer comme l'ion  $e^{-}$ , et il peut être modélisé par un porteur libre : le trou  $tr^{+}$ .

La densité atomique du Silicium cristallisé est  $N_{Si}$ . La densité de paires électrons-trous libres à la température normale est  $n_i = p_i$ . L'indice i signifie que le Silicium est pur (intrinsèque).  $n_i$  et  $p_i$  varient très fortement avec la température (voir la valeur de ces paramètres dans le tableau 2.3).

Dans un semi-conducteur il existe donc deux types de courant : un courant d'électrons et un courant de trous. Notons enfin que la charge du trou est égale à l'opposé de celle de l'électron :  $q_{tr} = -q_e = q$ .

| En résumé, pour le Silicium intrinsèque $(T = 300K)$                        |                                                                                           |  |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|

| la densité des $e^-$ libres est égale à celle des $tr^+$ libres : $n_i = p$ |                                                                                           |  |

| Technologie                                                                 | Résistance                                                                                |  |

| $N_{Si} = 50 \cdot 10^{27} m^{-3}$                                          |                                                                                           |  |

| $n_i = p_i = 15 \cdot 10^{+15} m^{-3}$                                      | $R = \frac{1}{q \cdot n_i \cdot (\mu_n + \mu_p)} \cdot \frac{L}{A_S} \approx 200 M\Omega$ |  |

| $\mu_n = 0,015m^2V^{-1}s^{-1}$                                              | $A_S \stackrel{\sim}{=} q \cdot n_i \cdot (\mu_n + \mu_p)  A_S \stackrel{\sim}{=} 200M32$ |  |

| $\mu_p = 0,006m^2V^{-1}s^{-1}$                                              |                                                                                           |  |

Tab. 2.3 – paramètres du Silicium pur

En utilisant les mêmes dimensions qu'au paragraphe 2.3.2 et les paramètres typiques d'une technologie CMOS  $0,5\mu m$  (voir le tableau 2.3), nous calculons la résistance du tube de Silicium pur.

#### Semi-conducteur dopé N

Le dopage N consiste à remplacer un certain nombre d'atomes de Silicium par des atomes donneurs en concentration  $N_D$ . Ces atomes possédent 5 électrons sur leur couche périphérique. Ils appartiennent donc à la colonne V de la classification périodique des éléments.

Quatre des cinq électrons périphériques des atomes donneurs participent aux liaisons covalentes avec les 4 atomes de Silicium voisins. Il suffit d'une énergie très faible pour que le 5<sup>e</sup> électron se libère. L'atome dopant de type N est ainsi un donneur (D) d'électron libre.

À 0K aucun atome du cristal de Silicium dopé n'est ionisé, il n'y a pas de porteur libre. À la température normale :

- certains atomes de Silicium s'ionisent, libérant chacun un électron et un trou libres appelés porteurs intrinsèques (même phénomène thermique que pour le Silicium pur),

- tous les atomes dopants s'ionisent, libérant chacun un électron et laissant chacun un atome fixe chargé positivement.

Le dopage de type N crée ainsi un déséquilibre entre les densités de porteurs libres :

- les porteurs majotitaires sont les électrons de densité :  $n_N \approx N_D$ ,

- les porteurs minotitaires sont les trous de densité :  $p_N \approx \frac{n_i^2}{N_D}$ ,

La densité de dopage N couramment utilisée pour les sources et les drains est typiquement :  $N_D = N_S = 10 \cdot 10^{+24} m^{-3}$ .

De même la densité de dopage N des substrats (Bulk, caisson) :  $N_B = 150 \cdot 10^{+21} m^{-3}$ .

Ceci est à comparer avec la concentration des porteurs intrinsèques :  $n_i=p_i=15\cdot 10^{+15}m^{-3}$ .

Rappelons enfin, la densité atomique du Silicium :  $N_{Si} = 50 \cdot 10^{+27} m^{-3}$ .

La neutralité électronique se vérifie en effectuant le bilan des charges :

- les charges positives sont :

- les trous libres  $p_N$ ,

- les atomes dopants ionisés fixes  $N_D$ .

- charges négatives sont :

- les électrons libres $n_N$ .

Dans les mêmes conditions qu'au paragraphe précédent nous calculons la résistance du tube de Silicium dopé N (tableau 2.4).

| En résumé, pour le Silicium dopé N $(T = 300K)$                                                   |                                                                                    |  |

|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|

| les $e^-$ sont majoritaires les $tr^+$ sont minoritaires : $n_N \approx N_D \gg p_N$              |                                                                                    |  |

| Technologie Résistance                                                                            |                                                                                    |  |

| $N_D = 70 \cdot 10^{21} m^{-3}$ $R \approx \frac{1}{10^{-3}} \cdot \frac{L}{10^{-3}} \approx 600$ |                                                                                    |  |

| $\mu_N = 0,015m^2V^{-1}s^{-1}$                                                                    | $R \approx \frac{1}{q \cdot N_D \cdot \mu_N} \cdot \frac{L}{A_S} \approx 60\Omega$ |  |

Tab. 2.4 – paramètres du Silicium dopé N

#### Semi-conducteur dopé P

Le dopage P consiste à remplacer un certain nombre d'atomes de Silicium par des atomes accepteurs en concentration  $N_A$ . Ces atomes possédent 3 électrons sur leur couche périphérique. Ils appartiennent donc à la colonne III de la classification périodique des éléments.

Quatre places sont disponibles pour les liaisons covalentes de la maille élémentaire de Silicium. Les trois électrons périphériques des atomes accepteurs participent à ces liaisons. Il suffit d'une énergie très faible pour qu'un  $4^{e}$  électron soit "emprunté" à un atome de Silicium voisin, qui se trouve ainsi ionisé  $Si^{+}$ , c'est à dire transformé en trou libre. L'atome dopant de type P est ainsi un accepteur (A) d'électron, un donneur de trou libre.

À 0K aucun atome du cristal de Silicium dopé n'est ionisé, il n'y a pas de porteur libre. À la température normale :

- certains atomes de Silicium s'ionisent, libérant chacun un électron et un trou libres appelés porteurs intrinsèques (même phénomène thermique que pour le Silicium pur),

- tous les atomes dopants s'ionisent, produisant chacun un trou et laissant chacun un atome fixe chargé négativement.

Le dopage de type P crée ainsi un déséquilibre entre les densités de porteurs libres :

- les porteurs majotitaires sont les trous de densité :  $p_P \approx N_A$ ,

- les porteurs minotitaires sont les électrons de densité :  $n_P \approx \frac{n_i^2}{N_A}$ ,

Les ordres de grandeur des densités de dopage sont les mêmes que précédemment. La neutralité électronique se vérifie de la même manière que précédemment.

Dans les mêmes conditions qu'au paragraphe 2.3.2 nous calculons la résistance du tube de Silicium dopé P (tableau 2.5).

| En résumé, pour le Silicium dopé P $(T = 300K)$                                      |                                                                               |  |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|

| les $tr^+$ sont majoritaires les $e^-$ sont minoritaires : $p_P \approx N_A \gg n_P$ |                                                                               |  |

| Technologie Résistance                                                               |                                                                               |  |

| $N_A = 70 \cdot 10^{21} m^{-3}$                                                      | $R \approx \frac{1}{N} \cdot \frac{L}{4} \approx 150\Omega$                   |  |

| $\mu_P = 0,006m^2V^{-1}s^{-1}$                                                       | $R pprox rac{1}{q \cdot N_A \cdot \mu_P} \cdot rac{1}{A_S} pprox 150\Omega$ |  |

Tab. 2.5 – paramètres du Silicium dopé P

Notons que les deux dernières résistances sont dans le rapport inverse des mobilités.

**Première conclusion** : nous pouvons faire varier la résistance d'un matériau en y faisant varier la densité des porteurs libres. À la construction du matériau, et une fois pour toute, ceci est obtenu en ajustant la densité de dopage.

#### 2.3.3 La jonction PN

L'interface entre deux zones semi-conductrices, l'une dopée N et l'autre dopée P, est appelée *jonction PN diode*. L'anode (A) correspond à la zone dopée P, la cathode (K) à la zone dopée N.

#### Mode de fonctionnement

Polarisation directe : si  $V_{PN}$  est positive la diode est polarisée en direct elle est passante, car un courant important la traverse (voir le modèle du courant).

Polarisation inverse : si  $V_{PN}$  est négative la diode est polarisée en inverse ou bloquée, car un courant extrêmement faible la traverse (voir le modèle du courant).

#### Modèle du courant

C'est le modèle de Shockley basé sur la modélisation du courant de diffusion :

$$I_j = A_j \cdot J_s \cdot \left( e^{\frac{V_{PN}}{u_{th}}} - 1 \right) \tag{2.1}$$

- l'aire de la jonction PN (l'interface P-N) :  $A_i$

- la densité du courant de saturation inverse, caractéristique de la technologie :  $J_s \approx 1~aA \cdot \mu m^{-2}$

- le potentiel thermodynamique à  $T = 300K : u_{th} \approx 26mV$

Rappelons l'équation :

$$J_s = q \cdot \left( \frac{D_n}{L_n} \frac{n_i^2}{N_A} + \frac{D_p}{L_p} \frac{n_i^2}{N_D} \right)$$

- Charge élémentaire :  $q = |q_{e-}| \approx 0, 16 \ aC$

- Densité de paires  $e^- tr^+$  dans le Si intrinsèque (pur) à 300 K :  $n_i \approx 14, 5 \cdot 10^{+15} m^{-3}$

- Densité de dopage N (donneurs, valeur typique) :  $N_D = 10 \cdot 10^{+21} \ m^{-3}$

- Densité de dopage P (accepteurs, valeur typique) :  $N_A = 10 \cdot 10^{+24} \ m^{-3}$

- Constante de diffusion des électrons dans le SiP :  $D_n = \mu_n \cdot u_{th}$

- Constante de diffusion des trous dans le SiN :  $D_p = \mu_p \cdot u_{th}$

- Longueur de diffusion (Debye) des électrons dans le SiP :  $L_n$

- Longueur de diffusion (Debye) des trous dans le SiN :  $L_p$

- Constante de Boltzmann :  $k=13, 8\cdot 10^{-24}\ J\cdot K^{-1}$

- Température ambiante :  $T \approx 300K$

#### Notons que:

- en direct avec  $V_{PN} \gg u_{th}$ , le courant varie exponentiellement et nous obtenons un décuplement de l'intensité tout les 60mV :  $I_{j_{(V_{PN}+60mV)}}=10\cdot I_{j_{(V_{PN})}},$  en inverse l'intensité est extrêmement faible et quasiment constante :  $I_{j}\approx -A_{j}\cdot J_{s}.$

Seconde conclusion : la diode est bien un élément "actif", c'est à dire qui se comporte comme un interrupteur commandé et dont la caractéristique en courant, quand il existe, n'est pas simplement ohmique (résistive), mais ce n'est pas une transconductance, car le dipôle de commande est confondu au dipôle de sortie.

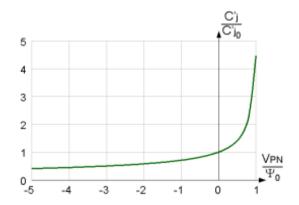

#### Modèle capacitif

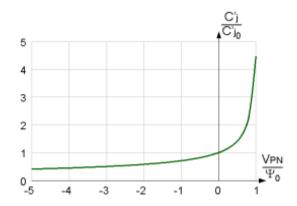

Le modèle capacitif de la jonction ne sera ici présenté que pour la polarisation inverse car le transistor MOS est constitué de jonctions toutes polarisées à  $V_{PN} \leq 0$  en mode de fonctionnement normal.

En polarisation inverse, il se forme autour de l'interface des deux zones dopées une région, appelée zone déserte, où la densité de porteurs libres est quasiment nulle. Elle se comporte comme un isolant qui constitue le diélectrique de la capacité équivalente  $C_i$ . L'épaisseur de la zone déserte  $x_D = f(V_{PN})$  dépend de  $V_{PN}$ . Sa valeur est minimale pour  $V_{PN} = 0V$  alors la valeur de la capacité est maximale.

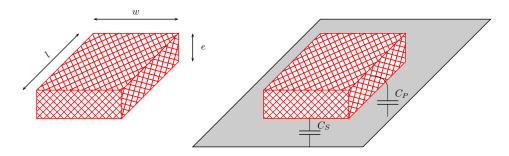

| En résumé, la jonction PN en inverse $V_{PN} \leq 0$ |                                     |                                  |

|------------------------------------------------------|-------------------------------------|----------------------------------|

| Coupe                                                | e technologique                     | Schéma équivalent                |

| W P                                                  | L V <sub>PN</sub>                   | P C <sub>J</sub> V <sub>PN</sub> |

| Dimensions                                           | Technologie                         | Modèle                           |

| $A_j = W \cdot L$                                    | $C'_{j0} = 0.8 fF \cdot \mu m^{-2}$ | $C_j = A_j \cdot C'_{j0}$        |

Tab. 2.6 – paramètres d'une jonction PN en technologie CMOS  $0,5\mu m$

Rappelons l'expression de la capacité surfacique à  $V_{PN}=0$   $V:Cj_{0}'=\sqrt{\frac{q\cdot\kappa_{s}\cdot\varepsilon_{0}}{2\cdot\Psi_{0}}\frac{1}{\frac{1}{N_{A}}+\frac{1}{N_{D}}}}$

- Constante diélectrique (permittivité relative) du silicium :  $\kappa_s \approx 11, 8$

- Permittivité du vide :  $\varepsilon_0 \approx 8,85 \ pF \cdot m^{-1}$

- Potentiel interne d'une jonction PN :  $\Psi_0 = u_{th} \cdot \ln \frac{N_A \cdot N_D}{n^2}$ valeur typique :  $\Psi_0 \approx +0.9 V$

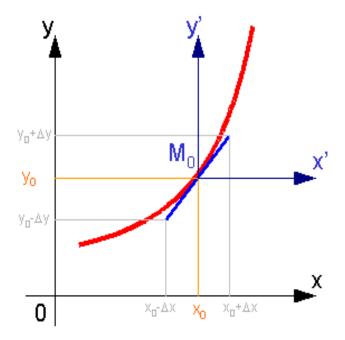

Fig. 2.3 – variation de la capacité en fonction de la polarisation

Rappelons l'expression de la capacité surfacique pour  $V_{PN} < \Psi_0 : Cj' = \frac{Cj_0'}{\sqrt{1 - \frac{V_{PN}}{\Psi_0}}}$

Cette équation est représentée par la courbe de la figure 2.3

#### 2.4 Composants MOS

Les matériaux étudiés au paragraphe 2.3.2 nous permettent de créer des dipôles de résistance fixe une fois choisie leur technologie et déterminées leurs dimensions. Si un potentiel est appliqué à leurs bornes et qu'il ne produit pas un champ électrique trop élevé (environ  $5MV \cdot m^{-1}$ , soit  $5V \cdot \mu m^{-1}$ ) la loi d'Ohm,  $V = R \cdot I$ , peut s'appliquer et permettre de calculer le courant traversant le dipôle c'est la première solution décrite ci dessous.

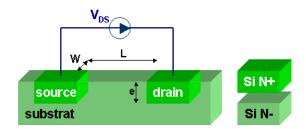

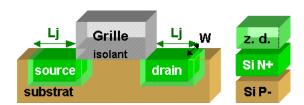

#### 2.4.1 Première étape : la résistance

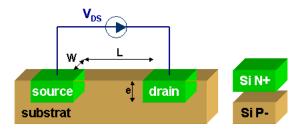

Dans un barreau de Silicium faiblement dopé N (Si N-), le  $suBstrat\ B$  (bulk en anglais), disposons deux prises de contact de Silicium fortement dopées N (Si N+) : la  $source\ (S)$  et le  $drain\ (D)$  (voir figure 2.4).

Fig. 2.4 – Résistance en technologie MOS

Ces 3 zones sont dopées de même type. Nous pouvons y faire circuler un courant formé majoritairement d'électrons qui s'écoulent de la source vers le drain, par conduction due au champ électrique longitudinal engendré par  $V_{DS}$ .

Les dimensions (la largeur W, la longueur L et l'épaisseur e) de la partie du substrat située entre D et S, et les paramètres technologiques du matériau dont est fait le substrat, déterminent la résistance équivalente  $R_{DS}$  ainsi que nous l'avons fait au paragraphe 2.3.2, et nous obtenons :  $V_{DS} = R_{DS}I_{DS}$ .

Nous n'avons pas de moyen externe au dipôle DS de commander l'intensité  $I_{DS}$ .

#### 2.4.2 Seconde étape : la diode

Utilisons maintenant un substrat de Silicium faiblement dopé P (Si P-). Appliquons la même polarisation que précédemment (voir figure 2.5). Les deux diodes DS et DB sont respectivement polarisées l'une à 0V l'autre en inverse, aucun courant ne peut traverser ces dipôles.

Fig. 2.5 – Diodes en technologie MOS

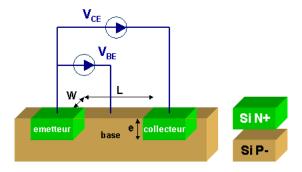

#### 2.4.3 Troisième étape : le transistor bipolaire

Sur la structure précédemment décrite, où momentanément, nous appellerons la Source "Émetteur" (E), et le Drain "Collecteur" (C), créons une troisième connexion la "Base" (B), pour polariser en direct la jonction BE. Nous venons de construire un transistor bipolaire où la zone P la Base (B) : voir figure 2.6 commande le courant.

Fig. 2.6 – Transistor bipolaire en technologie MOS

La tension  $V_{BE}$  (quelques dixièmes de Volts) commande le courant de la jonction BE (en direct). Des électrons sont injectés massivement dans la Base où ils sont minoritaires. La tension  $V_{CE}$  (de quelques Volts à quelques dizaines de volts) est telle que la jonction BC est fortement polarisée en inverse, ce qui "détourne" les électrons du courant  $I_{BE}$  injectés dans la Base, vers le Collecteur et crée un courant  $I_{CE}$  entre Collecteur et Émetteur.

Nous avons réalisé un dispositif modulant le courant de sortie  $I_{CE}$ , par la tension d'entrée  $V_{BE}$ . Il s'agit bien d'une transconductance, malheureusement il existe un courant parasite (les trous de  $I_{BE}$ ) en l'entrée (la base). L'étape suivante consiste à isoler cette entrée afin d'annuler l'intensité du courant parasite d'entrée.

#### 2.5 Le transistor MOS

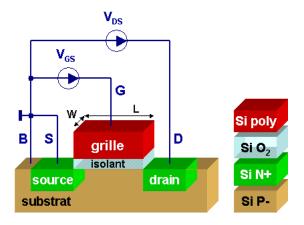

#### Quatrième étape : le transistor MOS

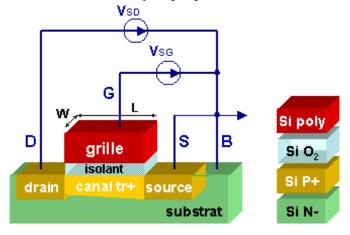

La quatrième étape consiste à faire croitre, au-dessus de la partie du substrat (du **S**emi conducteur Si faiblement dopé P) comprise entre Source et Drain, une couche fine d'isolant : de la silice ( $\mathbf{O}$ xyde de Silicium,  $SiO_2$ ). Sur cet isolant déposons une couche conductrice : du

Métal, comme dans le temps, ou du Silicium très fortement dopé donc poly-cristallin, appelé polysilicium (poly) tel que cela est fait maintenant. Appelons grille (G) la couche conductrice de polysilicium, et notons les initiales de ces 3 matériaux : MOS (voir figure 2.7).

Fig. 2.7 – le transistor MOS

La structure grille-isolant-substrat est une  $capacité\ MOS$  formée de :

- un isolant:

- d'épaisseur :  $t_{ox}$ ,

- de permittivité relative :  $\kappa_{ox} = 3,9$

- de capacité surfacique :  $C'_{ox} = \frac{\kappa_{ox} \cdot \varepsilon_0}{t_{ox}}$

- où la permittivité du vide est :  $\varepsilon_0 = 8,854pF \cdot m^{-1}$

- entre deux plaques conductrices (armatures) : la Grille et le suBstrat.

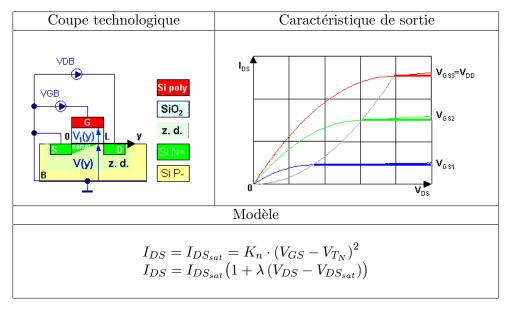

#### 2.5.1 Le fonctionnement des transistors CMOS

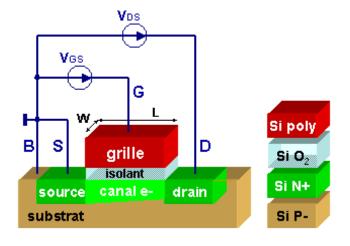

#### Le transistor MOS à canal N

- $V_{T_N}$  est la tension de seuil du NMOS. Elle est caractéristique de la technologie dans laquelle le transistor est construit. Typiquement :  $+0, 2V < V_{T_N} < +2V$

- Si  $V_{GS} > V_{T_N}$ , le canal existe, le NMOS est passant.

- Si  $V_{GS} \leq V_{T_N}$ , le canal n'existe pas, le NMOS est bloqué.

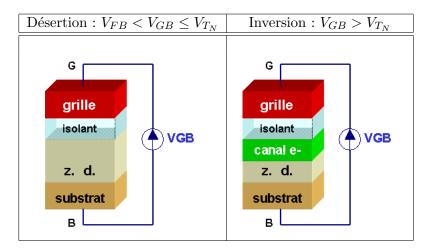

L'application d'une tension  $V_{GB}$  supérieure à  $V_{TN}$  aux bornes du condensateur  $C_{GB}$  entraîne l'apparition de charges positives sur la Grille et de charges de signe opposé  $(e^-)$  dans le substrat P. Une zone de type N, le canal (zone d'inversion), apparaît ainsi dans le substrat P. Une pseudo continuité N existe entre la Source et le Drain. Les électrons du canal se déplacent de la Source vers le Drain par la conduction engendrée par le champ électrique longitudinal lui même créé par  $V_{DS}$ . Il s'agit d'un transistor NMOS, c'est à dire un transistor MOS à canal N (canal d'électrons).

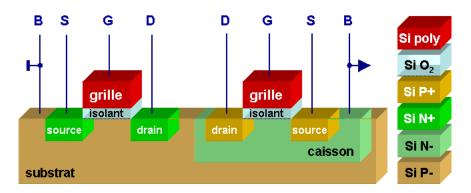

#### Le transistor MOS à canal P

Construisons le dual du transistor NMOS le transistor PMOS. Le substrat est faiblement dopé N (Si N-). Source et Drain sont fortement dopées P (Si P+). Isolant et Grille sont construits de la même façon que pour le NMOS.

- $V_{T_P}$  est la tension de seuil du PMOS. Elle est caractéristique de la technologie dans laquelle il est construit. Typiquement :

- $-2V < V_{T_P} < -0.2V$

- Si  $V_{GS} < V_{T_P}$ , le canal existe, le PMOS est passant.

- Si  $V_{GS} \ge V_{T_P}$ , le canal n'existe pas, le PMOS est bloqué.

L'application d'une tension  $V_{GB}$  inférieure à  $V_{TN}$  aux bornes du condensateur  $C_{GB}$  entraîne l'apparition de charges négatives sur la Grille et de charges de signe opposé  $(tr^+)$  dans le substrat N. Une zone de type P, le canal (zone d'inversion), apparaît ainsi dans le substrat N. Une pseudo continuité P existe entre la Source et le Drain. Les trous du canal se déplacent de la Source vers le Drain par la conduction engendrée par le champ électrique longitudinal lui même créé par  $V_{DS}$ . Il s'agit d'un transistor PMOS, c'est à dire un transistor MOS à canal P (canal de trous).

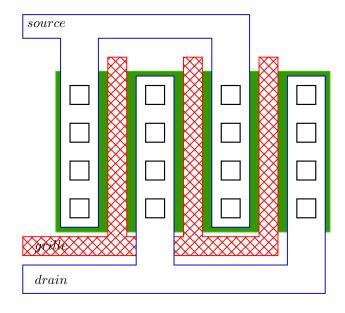

#### La technologie CMOS

Le C de CMOS veut dire Complémentaire. Une technologie CMOS est un procédé qui permet d'obtenir, dans un même monocristal (sur une même puce de Silicium), des transistors NMOS et des transistors PMOS. Le substrat d'une technologie CMOS est faiblement dopé P (nous pouvons y graver directement des NMOS). Le substrat N (pour graver les PMOS) est une zone faiblement dopée N (Si N-) : le caisson, dans le substrat (Si P-).

Fig. 2.8 – Coupe simplifiée d'une technologie CMOS

#### Troisième conclusion

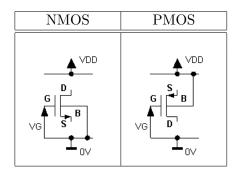

#### 2.5.2 Connexions des transistors

• Le caisson dopé N- (le substrat B) des PMOS leurs est commun. Il est polarisé à la tension la plus positive du circuit :  $V_{DD}$ ,

Tab. 2.7 – Connexions des transistors CMOS

- Le substrat (B) dopé P- des NMOS leurs est commun. Il est polarisé à la tension la plus négative du circuit :  $V_{SS} = 0V$  parfois  $V_{SS} = -V_{DD}$ ,

- Le Drain (D) des transistors NMOS est toujours polarisé à une tension supérieure à celle de leur Source (S),

- Le Drain (D) des transistors PMOS est toujours polarisé à une tension inférieure à celle de leur Source (S).

#### 2.6 Modèle électrique

Dans ce qui suit, nous nous efforcerons d'expliquer les phénomènes mis en jeu pour le cas du transistor NMOS. Nous n'élaborerons pas les équations, pour cela nous pouvons nous référer aux Leçons des modules SC ou PST, aux TD du module SC, ou à la bibliographie (voir 2.8). Pour le transistor PMOS nous nous contenterons de présenter les modèles.

#### 2.6.1 Les jonctions

Fig. 2.9 – Jonctions DB et SB isolées

Les jonctions source-substrat (SB) et drain-substrat (DB) sont des diodes à polarisation nulle ou inverse. Il se développe donc de part et d'autre de l'interface N-P, une zone déserte (z. d.) qui les isole du reste du substrat.

Cependant un courant de fuite extrêmement faible mais non nul, circule au travers de ces jonctions. Ce courant peut-être non négligeable dans certaines applications comme le point mémoire d'une DRAM.

#### 2.6.2 Formation du canal : la capacité MOS $C_{GB}$

Pour comprendre le phénomène de formation du canal d' $e^-$  dans le substrat P entre source et drain, considérons la capacité MOS Grille-suBstrat  $C_{GB}$  évoquée au paragraphe 2.5. La grille et le substrat jouent le rôle des armatures conductrices du condensateur et l'isolant de grille celui du diélectrique. Nous allons étudier son comportement statique, c'est à dire pour des variations lentes de  $V_{GB}$ . Attention le modèle utilisé ici ne peut s'appliquer que pour le cas de la formation du canal.

La capacité surfacique de l'isolant est  $C'_{ox} = \frac{\varepsilon_0 \cdot \kappa_{ox}}{t_{ox}}$ , où :

| Coupe technologique |                                               | Modèle                             |

|---------------------|-----------------------------------------------|------------------------------------|

|                     | grille sisolant Si O <sub>2</sub> substrat  B | Ф——                                |

| Dimensions          | Technologie                                   | Capacité maximale                  |

| W                   | épaisseur de l'isolant de grille :            |                                    |

|                     | $t_{ox} = 10nm$                               | $C_{GB} = W \cdot L \cdot C'_{or}$ |

| L                   | capacité surfacique de l'isolant de grille :  | $GB - W \cdot L \cdot C_{ox}$      |

|                     | $C'_{ox} = 3,5 fF \cdot \mu m^{-2}$           |                                    |

Tab. 2.8 – La capacité MOS  $C_{GB}$

- constantes physiques :

- permittivité du vide :  $\varepsilon_0 = 8,854pF \cdot m^{-1}$ ,

- permittivité relative de l'isolant de grille (oxyde de silicium :  $SiO_2$ ) :  $\kappa_{ox}=3,9$ .

- paramètre technologique (CMOS  $0, 5\mu m$ ):

- épaisseur de l'isolant de grille :  $t_{ox} = 10nm$ .

L'application d'une tension  $V_{GB}$  sur les armatures du condensateur  $C_{GB}$  engendre l'apparition de charges en quantités de valeurs absolues égales :

- positives sur l'armature connectée au pôle + du générateur  $V_{GB}$ ,

- négatives sur l'armature opposée, connectée au pôle du générateur.  $V_{GB}$  Notons les valeurs particulières de  $V_{GB}$  caractéristiques de la technologie :

- $V_{FB}$  typiquement :  $-0.5V < V_{FB} < +0.5V$ , la tension de "bande plate".

- $V_{T_N}$  typiquement :  $+0, 2V < V_{T_N} < +2V,$  la tension de seuil.

Etudions maintenant l'action de  $V_{GB}$  sur  $C_{GB}$  et sur la présence de porteurs libres.

#### Transistor bloqué : voir tableau 2.9

Tab. 2.9 – Régimes de la capacité MOS

Une quantité  $Q_g$  de charges libres positives est injectée sur la grille. Une quantité  $Q_d$

de charges négatives apparaît sur l'autre armature du condensateur  $C_{GB}$  dans le substrat Si P-. Ces dernières proviennent de la désertion des  $tr^+$  majoritaires du substrat (charges libres positives) qui ont laissé les atomes accepteurs ionisés  $(A^-)$  fixes dans le monocristal. À cet endroit la densité de porteurs libres est donc nulle, c'est une zone déserte (z. d.). Nous disons que la couche de substrat sous l'isolant est en régime de désertion. Aucune continuité électrique n'est possible entre la source et le drain. Le transistor est bloqué.

#### Transistor passant (Canal créé) : voir tableau 2.9

Au-delà de  $V_{T_N}$ , la tension  $V_{GB}$  injecte sur la grille une quantité  $Q_g$  de charges libres positives qui dans le substrat est compensée par :

- $Q_d$  la charge d'espace (des atomes accepteurs ionisés  $A^-$  fixes) de la zone déserte,

- $Q_i$  la charge d'inversion du canal (les électrons libres situés sous l'isolant de grille, dans la zone désertée par les trous).

Le canal est considéré comme formé, les électrons sont devenus majoritaires, et nous disons que la couche sous l'isolant est en r'egime d'inversion.

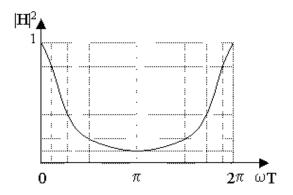

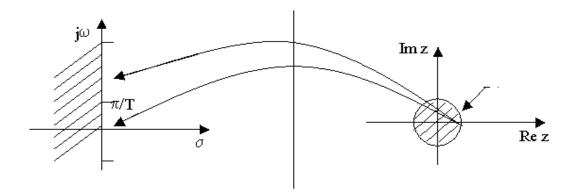

**Modèle capacitif de**  $C_{GB}$  : Nous obtenons entre **G**rille et su**B**strat deux capacités en série :  $C_{GC}$  (entre Grille et Canal) et  $C_{CB}$  (entre canal et suBstrat).  $C_{GC}$  est une capacité dite "géométrique" de valeur fixe  $(C_{GC} = C'_{ox} \cdot W \cdot L)$ .  $C_{CB}$  est une capacité dite "électrique" car sa valeur dépend de  $V_{GB}$ . La mesure du rapport  $C_{GB}/C_{GC} = f(V_{GB})$  permet d'extraire les paramètres technologiques  $V_T$  et  $V_{FB}$ .

#### 2.6.3 Le courant drain-source $(V_{GB} > V_{T_N})$

Le canal quand il existe, est un ensemble de charges libres mais statiques. Encore faut-il les entraı̂ner par l'action du champ électrique longitudinal entre drain et source (produit par  $V_{DS}$ ), pour obtenir un courant  $I_{DS}$ .

#### 2.6.4 Le condensateur élémentaire

Le canal existe, et le courant drain-source  $I_{DS}$  est un courant de conduction formé par :

- les charges libres injectées par l'effet capacitif du condensateur  $C_{GB}$  polarisé par la tension  $V_{GB}$ ,

- le champ électrique E le long du canal et créé par  $V_{DS}$  (pour le canal NMOS :  $V_D > V_S$ ). Nous nous contenterons ici, de modéliser la quantité élémentaire de charges libres le long du canal, afin d'identifier les principaux régimes de conduction du transistor.

Fig. 2.10 – Condensateur élémentaire  $c_{qb}$

#### 2.6.5 Calcul de $I_{DS}$

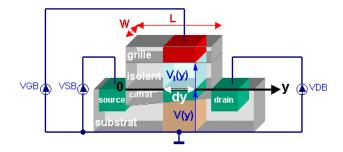

Choisissons un axe 0y le long du canal partant de la source (où y = 0) vers le drain (où y = L). Considérons un condensateur élémentaire  $c_{gb}$  de dimensions  $W \cdot dy$ , situé à la distance y de la source.

L'armature supérieure du condensateur élémentaire est constituée d'une portion équivalente de la grille et l'armature inférieure d'une portion équivalente du canal. L'application de la tension  $V_{GB}$  engendre une différence de potentiel  $V_I(y)$  aux bornes de l'isolant de grille. Rappelons que la couche d'inversion (le canal) est créée  $(V_{GB} > V_{T_N})$ , et que le bilan des densités de charges du condensateur élémentaire  $c_{qb}$  est :

- charges positives sur la grille élémentaire :  $dQ_q$ ,

- charges négatives dans le substrat :

- ions dopants fixes (charge d'éspace dans la zone déserte) :  $dQ_d$ ,

- électrons libres du canal :  $dQ_i$ .

- $dQ_q = -dQ_d dQ_i$

interrupteur fermé.

Calculons  $dQ_i(y)$  la densité des charges d'inversion :  $dQ_i(y) = -C'_{ox} \cdot W \cdot dy \cdot V_I(y)$ .

Pour  $V_{DS} \geq 0V$ ,  $V_I(y)$  n'est pas constante le long du canal. En effet, si le potentiel est le même sur toute la surface de grille (l'armature supérieure de  $C_{GB}$ ) la différence de potentiel  $V_{DS}$  le long du canal entre drain et source (l'armature inférieure) n'est pas nulle. Le canal n'est pas un conducteur, ce qui court-circuiterait drain et source, et en ferait un parfait

Soit V(y) le potentiel du substrat juste sous l'isolant, à la distance y de la source :  $V_{GB} = V_I(y) + V(y)$ .

V(y) augmente au fur et à mesure que l'on se déplace de la source vers le drain. Soient  $V_{SB}$  le potentiel de la source et  $V_{DB}$  celui du drain :

- $V(y=0) = V_{SB}$  près de la source,

- $V(y = L) = V_{DB}$  près du drain.

Ainsi la densité des électrons libres injectés dans le canal  $(V_{GB} > V_{T_N})$  est elle :

- $dQ_i(y) = -C'_{ox} \cdot W \cdot dy \cdot [V_{GB} V_{T_N} V(y)]$  en y entre source et drain (0<y<L),

- $dQ_i(y=0) = -C'_{ox} \cdot W \cdot dy \cdot [V_{GB} V_{T_N} V_{SB}]$  près de la source (y=0),

- $dQ_i(y = L) = -C'_{ox} \cdot W \cdot dy \cdot [V_{GB} V_{T_N} V_{DB}]$  près du drain (y=L).

Lorsque y croît de 0 à L, V(y) croît de  $V_{SB}$  à  $V_{DB}$ . Le facteur  $[V_{GB} - V_{T_N} - V(y)]$  décroît, de même que  $|dQ_i(y)|$ .

Supposons que la densité des porteurs libres soit constante dans la couche d'inversion (le canal). La décroissance de  $|dQ_i(y)|$  signifie que l'épaisseur du canal diminue de la source vers le drain.

Maintenant pour simplifier, nous imposons  $V_S = 0V$ . Alors  $V_{GB} = V_{GS}$ . La charge élémentaire d'inversion s'écrit :

•

$$dQ_i(y) = -C'_{ox} \cdot W \cdot dy \cdot [V_{GS} - V_{T_N} - V(y)]$$

y varie de 0 à L et V(y) varie de 0V à  $V_{DS}$ .  $|dQ_i(y)|$  diminue bien de la source vers le drain

Positionnons nous près du drain où  $V(y=L)=V_{DS}$ . Pour chaque  $V_{GS}$  il existe une valeur  $V_{DSsat}$  de  $V_{DS}$  telle que  $dQ_i(y=L)$  s'annule, c'est à dire pour laquelle l'épaisseur du canal est nulle (pincement du canal) :

•

$$dQ_i(y=L) = -C'_{ox} \cdot W \cdot dy \cdot (V_{GS} - V_{TN} - V_{DSsat}) = 0 \Rightarrow V_{DSsat} = V_{GS} - V_{TN}$$

$$\frac{dQ_i(y=L)}{dQ_i(y=L)} = -C'_{ox} \cdot W \cdot dy \cdot (V_{GS} - V_{T_N} - V_{DSsat})$$

$$\geqslant V_{DS_{sat}} = V_{GS} - V_{T_N}$$

(2.2)

$V_{DS_{sat}}$  est la tension de pincement ou tension de saturation, elle dépend de  $V_{GS}$ .

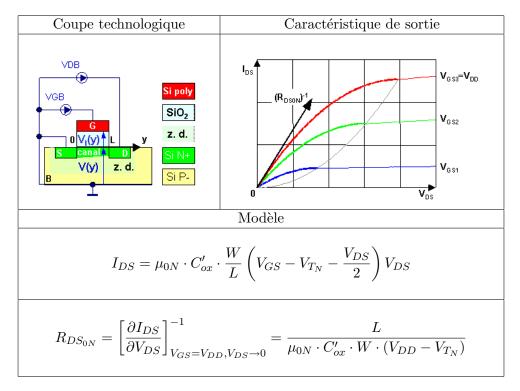

#### Régime quadratique : $V_{DS} < V_{GS} - V_{T_N}$

Soient:

- $q = |q_e|$  la charge élémentaire (en C Coulomb),

- $\mu_{0N}$  la mobilité des électrons dans le canal (en  $m^2 \cdot V^{-1} \cdot s^{-1}$ ),

- n la densité (constante) des électrons dans le canal (en  $m^{-3}$ ),

- $I_{DS}$  l'intensité (constante) du courant dans le canal (en A),

- s(y) l'aire de la section du canal en y (en  $m^2$ ),

- J(y) la densité du courant dans le canal en y (en  $A \cdot m^{-2}$ ),

- E(y) le champ électrique longitudinal en y, du à V(y) (en  $V \cdot m-1$ ).

Nous pouvons ainsi écrire:

- relation entre l'intensité et la densité de courant :  $I_{DS} = s(y) \cdot J(y)$

- définition de la densité du courant de conduction :  $J(y) = -n \cdot q \cdot \mu_{0N} \cdot E(y)$

- définition du champ électrique :  $E(y) = -\frac{dV(y)}{dy}$

- report dans l'expression de  $I_{DS}: I_{DS} = +n \cdot q \cdot \mu_{0N} \cdot s(y) \frac{dV(y)}{dy}$

- enfin:  $I_{DS} \cdot dy = +n \cdot q \cdot \mu_{0N} \cdot s(y) \cdot dV(y)$

Explicitons la charge élémentaire d'inversion  $dQ_i(y)$  en fonction des grandeurs définies plus haut:

- $dQ_i(y) = -n \cdot q \cdot s(y) \cdot dy = -C'_{ox} \cdot W \cdot dy \left[V_{GS} V_{T_N} V(y)\right]$

- $\bullet \Rightarrow n \cdot q \cdot s(y) = C'_{ox} \cdot W \cdot [V_{GS} V_{T_N} V(y)]$

Pour trouver  $I_{DS}$  nous intégrons le long du canal, c'est à dire pour y variant de 0 à L et pour V(y) variant de 0V a  $V_{DS}$ :

•  $I_{DS} \cdot dy = \mu_{0N} \cdot C'_{ox} \cdot \widetilde{W} \cdot [V_{GS} - V_{T_N} - V(y)] \cdot dV(y)$ Ce qui donne:

$$I_{DS} = \mu_{0N} \cdot C'_{ox} \cdot \frac{W}{L} \cdot \left( V_{GS} - V_{T_N} - \frac{V_{DS}}{2} \right) \cdot V_{DS}$$

$$(2.3)$$

D'autre part, à l'aide de la tangente à l'origine de la caractéristique  $I_{DS} = f(V_{DD}, V_{DS})$ , pour  $V_{GS} = V_{DD}$ , nous définissons la résistance  $R_{DS_{0N}}$ , qui nous sera utile dans le module ENI (voir le tableau 2.10).

Dans les tableaux suivant, nous utilisons les paramètres et les valeurs typiques d'une technologie CMOS  $0.5\mu m$  sur Silicium :

- le facteur de transconductance NMOS (propre à la technologie) :  $k_n = \mu_{0N} \cdot C'_{ox}$  le coefficient de conduction (propre au transistor) :  $K_n = \frac{k_n}{2} \frac{W}{L} = \frac{\mu_{0N} \cdot C'_{ox}}{2} \frac{W}{L}$

- le coefficient de modulation de longueur de canal (transistor) :  $\lambda \approx \frac{1}{V_F \cdot L}$  en  $V^{-1}$

- la tension d'Early (technologie) :  $V_E \approx 5MV \cdot m^{-1}$

- ainsi :  $\frac{\Delta L}{L} = \lambda \left( V_{DS} V_{DS_{sat}} \right)$  ou  $\Delta L = \frac{V_{DS} V_{DS_{sat}}}{V_E}$  la capacité surfacique de l'isolant de grille (technologie) :  $C'_{ox} \approx 3.5 fF \cdot \mu m^{-2}$

- la mobilité en surface des électrons (technologie) :  $\mu_{0N} \approx 14, 3 \cdot 10^{-3} m^{+2} V^{-1} s^{-1}$

- la tension de seuil (technologie) :  $V_{T_N} = +0,7V$

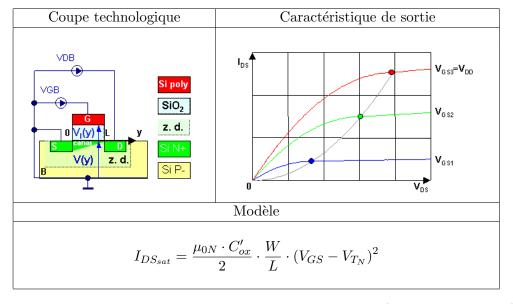

#### Régime de pincement : $V_{DS} = V_{DS_{sat}} = V_{GS} - V_{T_N}$

Lorsque  $V_{DS} = V_{DSsat}$ , l'épaisseur du canal est nulle au droit du drain (le point de pincement est en y = L).  $V_{DSsat}$  est la tension de saturation. Ce qui donne (tableau 2.11) :

$$I_{DS} = I_{DS_{sat}} = \frac{\mu_{0N} \cdot C'_{ox}}{2} \cdot \frac{W}{L} \cdot (V_{GS} - V_{T_N})^2$$

(2.4)

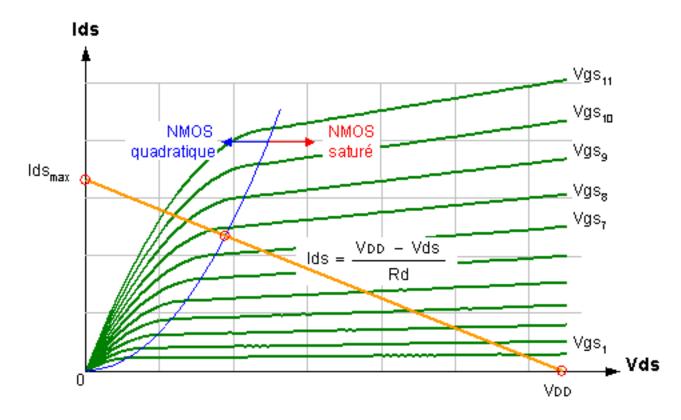

Tab. 2.10 – Transistor NMOS en régime quadratique

Tab. 2.11 – Transistor NMOS au pincement (point de saturation)

#### Régime de saturation : $V_{DS} > V_{DS_{sat}} = V_{GS} - V_{T_N}$

Lorsque  $V_{DS} > V_{GS} - V_{T_N}$ , le point de pincement se situe entre la source et le drain. Le transistor est saturé. Tous les électrons du canal sont happés par le fort champ électrique qui règne, le courant est à son maximum pour un  $V_{GS}$  donné, et n'augmente plus que faiblement avec  $V_{DS}$  (droites obliques en traits fins sur le graphe du tableau 2.12).

L'augmentation vient du fait que le canal est plus court :

- longueur du canal en régime quadratique ou au point de saturation : L

- longueur du canal en régime saturé :  $L \Delta L$  ainsi le facteur W/L devient il :  $\frac{W}{L} = \frac{W}{L \Delta L} = \frac{W}{L} \frac{1}{1 \frac{\Delta L}{L}} \approx \frac{W}{L} \left(1 + \frac{\Delta L}{L}\right)$

Nous supposons qu'entre le point de pincement et le drain, il n'y a aucune perte de porteur libre puisque la zone est déserte et qu'il n'y a ainsi aucune recombinaison.

Nous utiliserons deux modèles pour le régime saturé :

- modèle simple (non prise en compte de l'effet Early) :  $I_{DS} = I_{DS_{sat}}$  (droites horizontales en traits gras sur le graphe du tableau 2.12)

- prise en compte de l'effet Early (droites obliques en traits fins sur le graphe du tableau 2.12)

Tab. 2.12 – Transistor NMOS en régime saturé

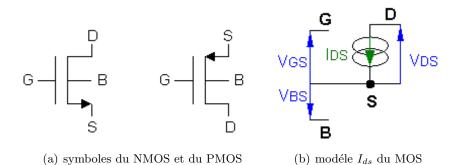

#### 2.6.6 Le courant $I_{DS}$ en résumé

NMOS : voir la table 2.13. PMOS : voir la table 2.14. Attention la tension de seuil du transistor PMOS  $V_{T_P}$  est négative! (voir paragraphe 2.5.1).

| Conditions           |                                                           | Régime                    | Courant                                                                                   |

|----------------------|-----------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------|

| $V_{GS} \le V_{T_N}$ | $\forall V_{DS}$                                          | bloqué                    | $I_{DS} = 0$                                                                              |

|                      | $V_{DS} < V_{DS_{sat}}$ $V_{DS_{sat}} = V_{GS} - V_{T_N}$ | quadratique               | $I_{DS} = +2K_n \left( V_{GS} - V_{T_N} - \frac{V_{DS}}{2} \right) V_{DS}$                |

| $V_{GS} > V_{T_N}$   | $V_{DS} = V_{DS_{sat}}$                                   | pincement                 | $I_{DS_{sat}} = +K_n \cdot (V_{GS} - V_{T_N})^2$                                          |

|                      | $V_{DS} > V_{DS_{sat}}$                                   | saturé                    | $I_{DS} = I_{DS_{sat}} \left( 1 + \lambda_n \left( V_{DS} - V_{DS_{sat}} \right) \right)$ |

| $V_{GS} = V_{DD}$    | $V_{DS} \approx 0$                                        | Résistance<br>équivalente | $R_{DS_{0N}} = \frac{1}{2K_n \cdot (V_{DD} - V_{T_N})}$                                   |

Tab. 2.13 – Courant et résistance équivalente du NMOS

| Conditions           |                                                           | Régime                    | Courant                                                                                   |

|----------------------|-----------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------|

| $V_{GS} \ge V_{T_P}$ | $\forall V_{DS}$                                          | bloqué                    | $I_{DS} = 0$                                                                              |

|                      | $V_{DS} > V_{DS_{sat}}$ $V_{DS_{sat}} = V_{GS} - V_{T_P}$ | quadratique               | $I_{DS} = -2K_p \left( V_{GS} - V_{T_P} - \frac{V_{DS}}{2} \right) V_{DS}$                |

| $V_{GS} < V_{T_P}$   | $V_{DS} = V_{DS_{sat}}$                                   | pincement                 | $I_{DS_{sat}} = -K_p \cdot (V_{GS} - V_{T_P})^2$                                          |

|                      | $V_{DS} < V_{DS_{sat}}$                                   | saturé                    | $I_{DS} = I_{DS_{sat}} \left( 1 + \lambda_p \left( V_{DS} - V_{DS_{sat}} \right) \right)$ |

| $V_{GS} = -V_{DD}$   | $V_{DS} \approx 0$                                        | Résistance<br>équivalente | $R_{DS_{0P}} = \frac{1}{2K_p \cdot (-V_{DD} - V_{T_P})}$                                  |

Tab. 2.14 – Courant et résistance équivalente du PMOS

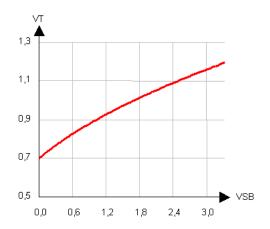

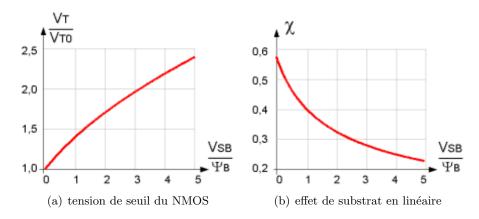

#### 2.6.7La tension de seuil

La tension de seuil d'un transistor MOS est une donnée technologique pour  $V_{SB} = 0V$ , elle est notée  $V_{T0}$ . La tension de seuil augmente lorsque  $V_{SB}$  augmente. Si  $V_{SB} > 0V$  la tension de seuil est notée  $V_T$ .

Soient les grandeurs suivantes :

- la densité de dopage du substrat :  $N_B$  (paramètre technologique en  $m^{-3}$ ),

- la capacité surfacique de l'isolant de grille :  $C'_{ox}$  (paramètre technologique en  $F \cdot m^{-2}$ ),

- la tension de bande plate :  $V_{FB}$  (paramètre technologique en V),

- la densité de paires électrons-trous libres dans le Silicium intrinsèque à  $T=300K:n_i$ (constante physique du Si en  $m^{-3}$ ),

- la permittivité du Silicium :  $\varepsilon_{Si}$  (constante physique du Si en  $F \cdot m^{-1}$ ),

- le potentiel thermodynamique à  $T = 300K : u_{th} = \frac{kT}{g}$  (constante physique en V),

- la charge élémentaire : q (constante physique en C Coulomb), le potentiel interne du substrat à l'inversion :  $\Psi_B = 2 \ u_{th} \cdot \ln \frac{N_B}{n_i}$ (constante technologique en V, si le substrat n'était pas dopé, c'est à dire s'il était fait de Silicium intrinsèque, nous aurions :  $N_B = ni$  et  $u_{th} \cdot \ln \frac{N_B}{ni} = 0V$ )

- le coefficient d'effet de substrat :  $\gamma = \frac{\sqrt{2q \cdot N_B \cdot \varepsilon_{Si}}}{C'_{or}}$  (constante technologique en  $\sqrt{V}$ ), Nous avons alors:

$$V_{T0} = V_{FB} + \Psi_B + \gamma \sqrt{\Psi_B} \tag{2.5}$$

$$V_T = V_{T0} + \gamma \left( \sqrt{\Psi_B - V_{BS}} - \sqrt{\Psi_B} \right) \tag{2.6}$$

Le plus souvent nous nous bornerons à utiliser le modèle graphique de la variation de  $V_T$  en fonction de  $V_{SB}$ , selon la courbe 2.11 obtenue pour les paramètres d'une technologie CMOS  $0,5\mu m$ . L'ordonnée à l'origine est  $V_{T0}$ .

Ce qui précède s'entend pour le transistor NMOS. En résumé l'évolution de la tension de seuil pour les 2 types de transistors est la suivante :

- transistor NMOS:

- $-V_{T0_N} > 0V$

- $-V_{BS_N} = 0V \Rightarrow V_{T_N} = V_{T0_N}$  $-V_{BS_N} < 0V \Rightarrow V_{T_N} > V_{T0_N}$

Fig. 2.11 – L'effet de substrat :  $V_T = V_{T0} + f(V_{SB})$

- transistor PMOS :

- $-V_{T0_P} < 0V$

- $-V_{BS_P} = 0V \Rightarrow V_{T_P} = V_{T0_P}$  $-V_{BS_P} > 0V \Rightarrow V_{T_P} < V_{T0_P}$

#### 2.6.8 Conclusion sur le courant $I_{DS}$

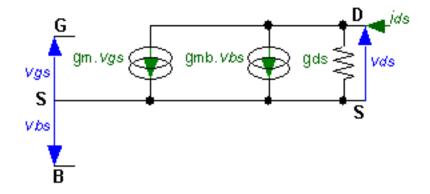

Le modèle du courant de sortie du transistor MOS que nous venons d'élaborer, est un ensemble de 3 équations correspondant à 3 régimes de fonctionnement. Lorsque le transistor est passant les équations dépendent de 3 variables électriques, les trois tensions aux bornes du transistor dont nous avons pris la Source comme référence :  $I_{DS} = f(V_{GS}, V_{BS}, V_{DS})$

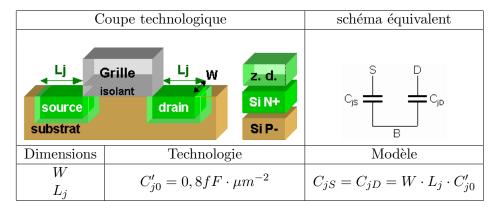

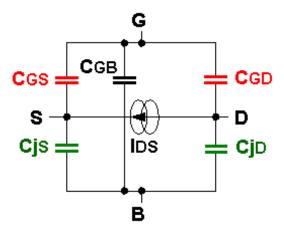

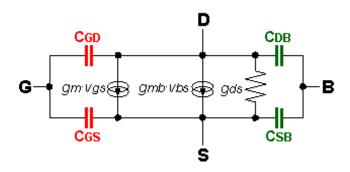

#### 2.6.9 Modélisation des capacités

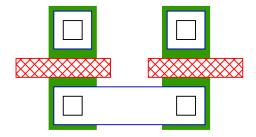

## Les jonctions

Les jonctions source-substrat (SB) et drain-substrat (DB) sont des diodes à polarisation nulle ou inverse. Il se développe donc de part et d'autre de l'interface N-P une zone déserte qui les isole du reste du substrat. Cette zone joue le rôle du diélectrique d'un condensateur (voir paragraphe 2.3.3. Ce diélectrique est du silicium déserté, dont la capacité surfacique maximale est  $C'_{i0}$  (paramètre technologique).

Tab. 2.15 – Capacités des jonctions du NMOS

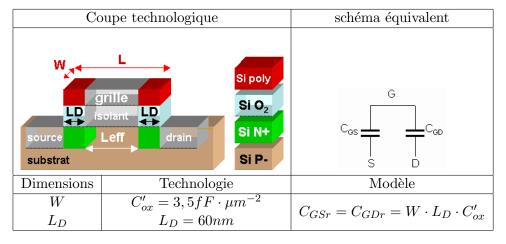

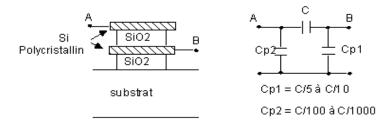

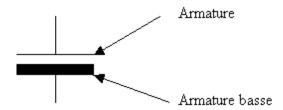

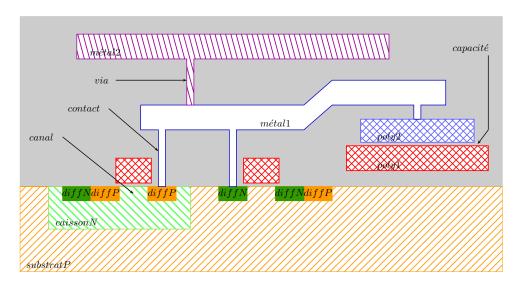

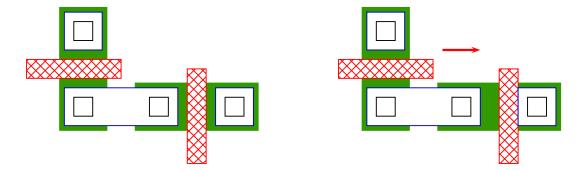

# Les capacités de débordement (recouvrement)

Les zones de source et de drain sont obtenues par implantation ionique des dopants dans le substrat. Sous l'effet de la température du recuit, qui a pour objectif de réorganiser la maille cristalline, les atomes dopants ont tendance à migrer sous la grille, qui leur préexiste. Ainsi les zones conductrices de source et de drain, débordent-elles sous l'isolant de grille, constituant l'armature inférieure de deux capacités d'oxyde dont l'armature supérieure, commune, est le polysilicium de grille (voir figure 2.16).

La longueur de débordement LD est une caractéristique de la technologie, elle est de l'ordre de quelques dizaines de nm.

Tab. 2.16 – Capacités des jonctions du NMOS

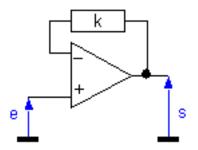

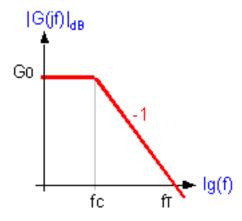

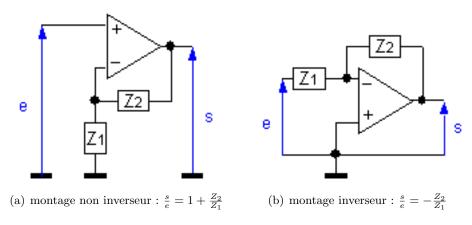

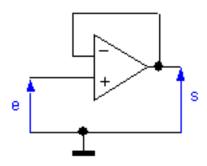

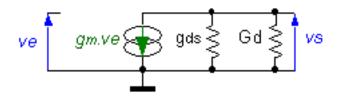

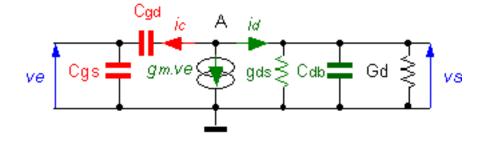

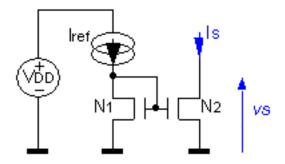

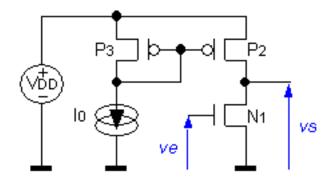

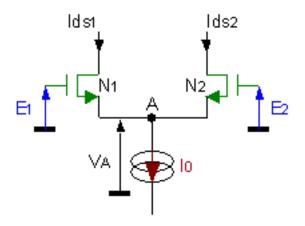

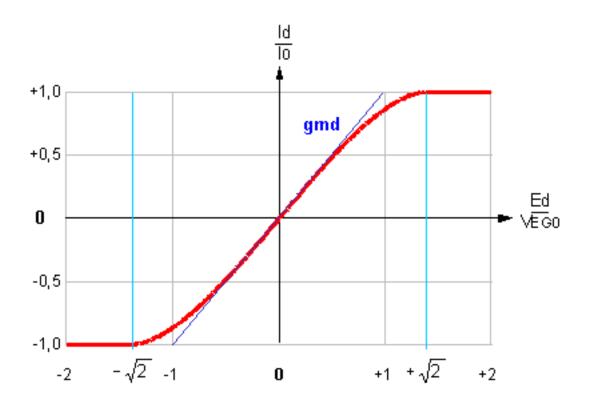

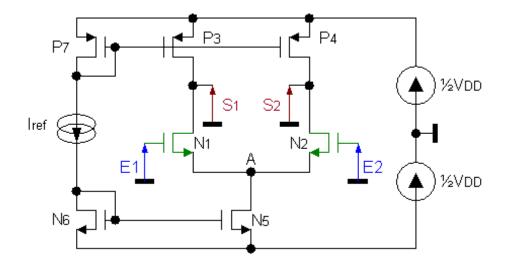

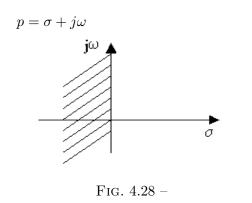

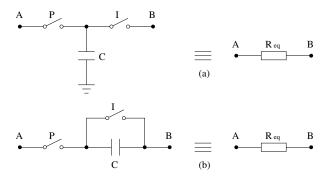

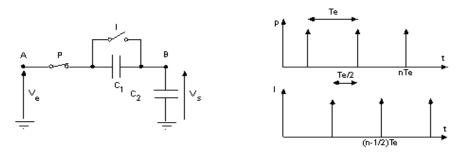

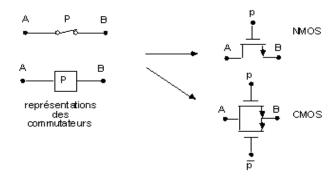

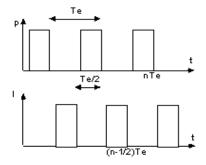

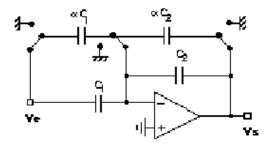

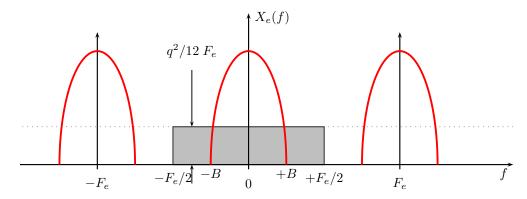

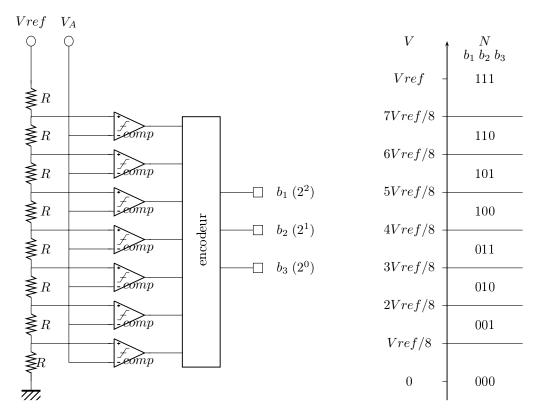

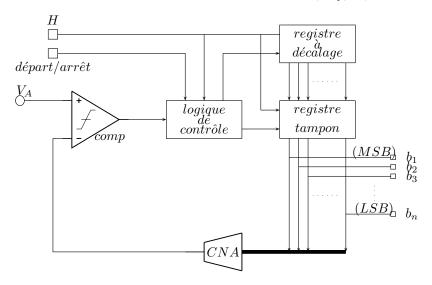

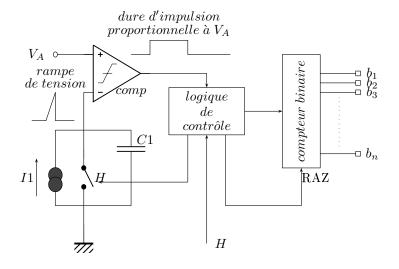

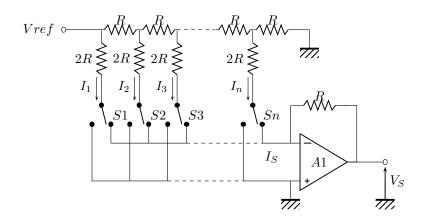

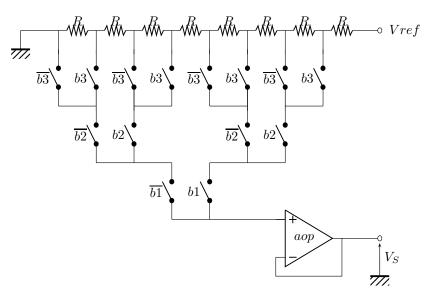

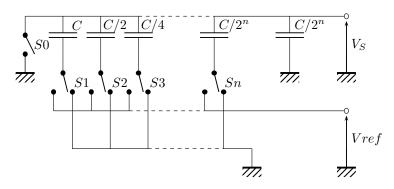

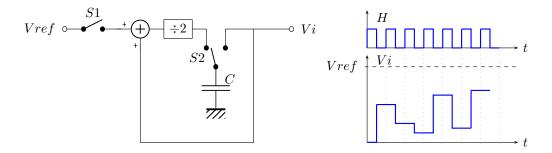

### La capacité grille-substrat