Systèmes configurables sur FPGA

2025-2026

Les FPGAs contiennent des ressources logiques configurables et ont toujours été utilisé comme véhicule de test et de prototypage. Ils ont été utilisés pour concevoir des accélérateurs “câblés” qui peuvent être reliés à un système de contrôle.

Avec l’augmentation de la taille de ces derniers, il est devenu envisageable d’implémenter un processeur complet, voir un SoC avec ces périphériques. Au-delà du test et du prototypage il devient envisageable de les utiliser pour certains types d’application nécessitant l’intégration poussée d’un système à base de processeur et des accélérateurs dédiés.

Les cycles de développement sur FPGA sont plus courts. Il est aussi possible de corriger un design et de le mettre à jour (ce qui n’est pas possible avec un ASIC).

Mais, le développement d’architectures numériques dédiées reste complexe et moins simple à aborder qu’un développement purement logiciel (du point de vue des ressources disponibles ou des compétences exigées).

L’idée étant d’utiliser les FPGA comme des systèmes conçus autour d’un processeur (et donc d’un flot de développement logiciel) que l’on peut spécialiser à volonté. Ceci permet de répondre à certains besoins extrêmement spécialisés, sans devoir développer un ASIC dédié et en gardant des coûts raisonnables, même pour des petites productions.

Reprendre les différents éléments internes d’un SoC ainsi que les techniques de développement associées.

Les intégrer en utilisant les ressources disponibles dans les FPGAs.

Il faut noter que: - les ressources internes des FPGA sont spécifiques, et donc une adaptation est souvent nécessaire, - les performances (vitesse/consommation) sur FPGA sont en deçà de ce qu’on peut obtenir avec un circuit dédié.

Dans la suite, nous présentons rapidement les solutions existantes pour la conception orientée SoC sur FPGA.

Utiliser les ressources du FPGA pour implémenter le processeur

Par contre,

Le fait de pouvoir implémenter ce genre de systèmes sur n’importe quel FPGA, permet d’avoir des systèmes génériques que l’on peut transposer d’une cible à l’autre et adapter à volonté. Ceci est intéressant quand on veut réutiliser le même système dans un contexte différent ou ne pas être dépendant des fournisseurs de circuits.

Il faut noter cependant que souvent les processeurs que spécial FPGA sont conçus un peu différemment pour prendre en compte les ressources disponibles. Aussi, ces processeurs ont souvent été conçus par les vendeurs de FPGA et sont différents des processeurs habituels auxquels on est habitués. Les performances sont aussi limitées et les ressources qui sont utilisées pour les implémenter seront prises dans le FPGA au détriment de l’application (ne vaut-il-pas mieux mettre un processeur externe?)

Dans ce qui suit, quelques exemples de solutions/produits existants.

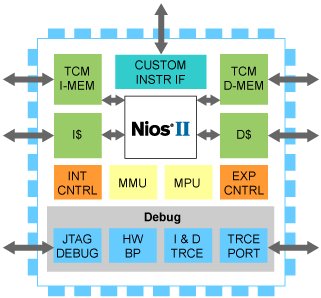

Xilinx et Altera (Intel FPGA) proposent des cœurs de processeurs destinés à être utilisés sur leur FPGA respectifs. Ces processeurs reprennent une architecture RISC standard et sont très similaires du point de vue des fonctionnalités offertes. Ils permettent de cibles des applications du type microcontrôleur et RTOS, mais peuvent aussi être configurés pour faire fonctionner Linux.

Ils sont fournis avec un environnement qui permet de les configurer en fonction des performances et objectifs de développement. Le code RTL n’est pas distribué, peuvent nécessiter de payer des licences et sont liés aux FPGA de chaque fabricant.

Bien que l’environnement logiciel autour de ces processeurs existe et est assez riche, ils restent assez exotiques, car limités aux seules cibles FPGAs.

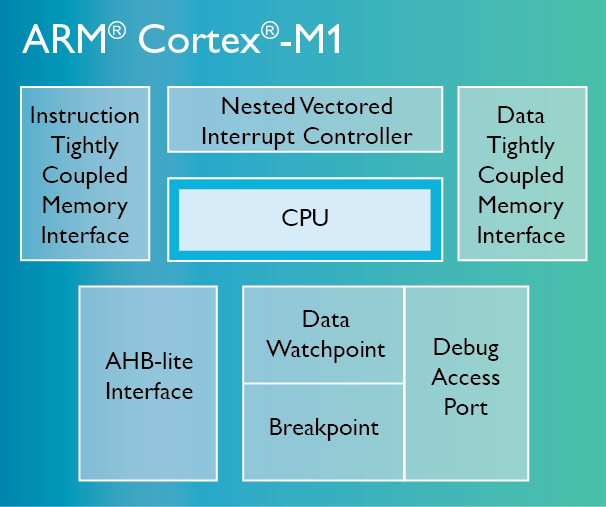

ARM propose des IPs un cœur de processeur spécialement conçus pour FPGA, le cortex M1. Proche du Cortex-M0, il permet de profiter de tout l’environnement logiciel associé au processeur embarqué ARM.

Ce cœur de processeur n’est pas lié à une marque de FPGAs, mais reste propriétaire.

Il existe aussi une version du Cortex-M3 pour les cibles FPGA.

Il existe d’autres initiatives plus ou moins maintenues, comme OpenCores et l’OpenRisc. OpenCore est un dépôt regroupant des IPs libre (free) et on peut y trouver des implémentations de cœurs processeurs (souvent anciens pour lesquels il n’y a plus de brevets) et de périphériques distribués librement. L’OpenRisc est un projet de processeur (jeu d’instruction plus implémentation de référence OR1200) qui n’a pas connu l’engouement que l’on observe actuellement avec le RISC-V.

Intel/Altera et AMD/Xilinx on entamé la transition vers cette architecture.

Démarrée en 2010, l’initiative RISC-V (5e génération de processeurs RISC), à pour but de définir les spécifications du jeu d’instruction d’un processeur de façon ouverte et collaborative. Une communauté active d’académiques et des industriels participent à la définition de cette spécification et de ces différentes extensions.

La spécification étant ouverte, libre de droit et sans brevets associés, il est possible de développer des implémentations libre et propriétaires. Le site officiel de la fondation RISC-V maintient une liste d’implémentations.

La spécification est modulaire, et elle couvre plusieurs cas d’usage allant du microprocesseur embarqué 32 bits au processeur applicatif 64 bits. Un mécanisme d’extensions, standards ou personnalisées, permet d’étendre le jeux d’instruction en fonction des besoins de l’application.

L’activité autour de cette architecture est très dynamique que ça soit du point de vue du développement matériel que logiciel. L’environnement logiciel est ainsi très riche, à jour et maintenu. Ceci entraine une transition certaine vers cette architecture pour les cœurs embarqués.

Ainsi, Intel propose maintenant, pour ces FPGA, le Nios V basé sur l’architecture RISC-V. Il est destiné, à remplacer le Nios II. De même, AMD, propose pour ces FPGA le Microblaze V.

Intégrer un vrai cœur de processeur dans un FPGA permet de bénéficier d’un processeur bien plus performant en termes de fréquence de fonctionnement et de consommation énergétique.

Historiquement, les fabriquant de FPGA ont intégré des cœurs RISC (ARM et PowerPC). Par exemple:

Ces produits ne sont plus commercialisés, et sont donnés ici à titre indicatif.

Le problème principal de ce type de solutions est le fait que ces cœurs de processeurs étaient nus et qu’il fallait construire le système autour en utilisant les ressources du FPGA. Il fallait dont programmer le FPGA avant de pouvoir les utiliser. Ceci posait des problèmes de cohérence et de stabilité de la plateforme et rendait les développements logiciels complexes.

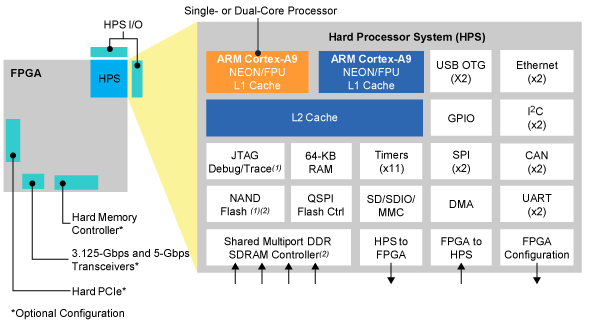

Avec l’augmentation des densités d’intégration, il est devenu possible d’intégrer en plus des cœurs de processeurs, un système complet.

Ces systèmes sont autonomes et peuvent fonctionner sans programmer le FPGA à priori. Une fois démarré, il est possible de programmer la zone FPGA à partir à partir du système.

Ceci simplifie les développements logiciels et la maintenance de bibliothèques et autres systèmes d’exploitation.

La partie FPGA servant à implémenter des accélérateurs spécifiques qui peuvent s’interfacer avec le SoC.

Il existe plusieurs déclinaisons de ce genre de Systèmes en voici quelques exemples.

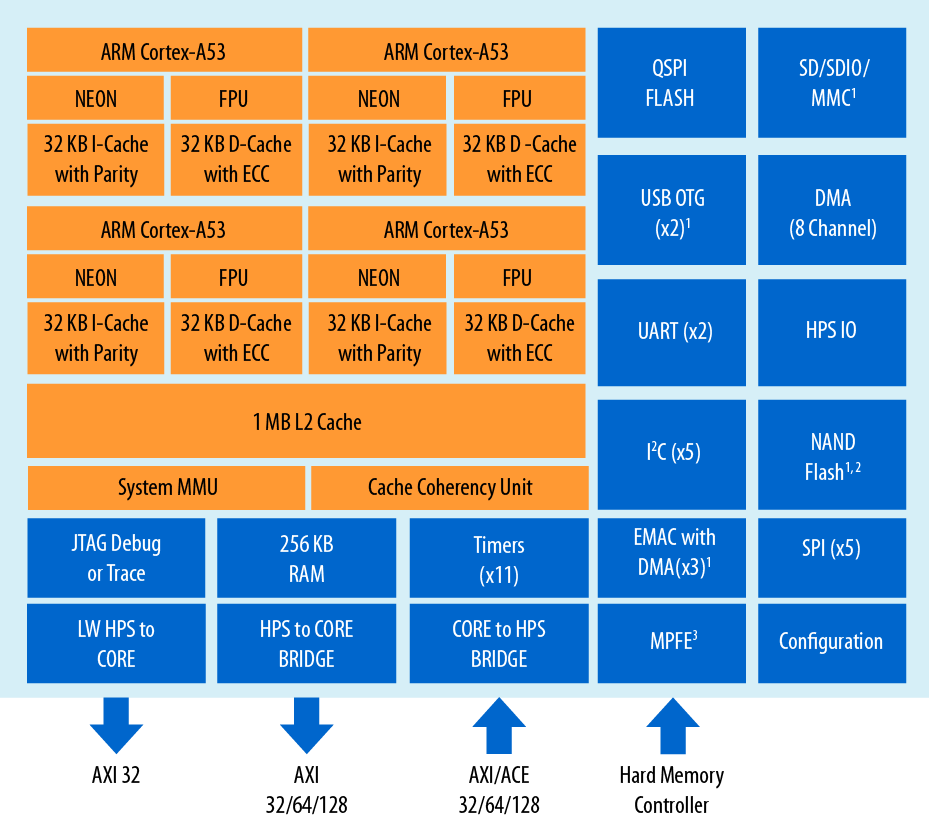

Système sur puce complet:

Zone FPGA connectée au bus du processeur

Système sur puce complet:

Zone FPGA connectée au bus du processeur

On constate qu’il y a un consensus chez les deux grands fabricants de FPGAs sur l’utilisation de systèmes basés sur des cœurs ARM. Ceci vient du fait que les ressources matérielles et logicielles associées sont bien maitrisées et maintenues.

Le support logiciel est aussi assuré et il est possible d’utiliser des distributions Linux pour ces plateformes. L’accès et la programmation de la partie FPGA à partir du Linux embarqué et aussi possible.

Les interfaces entre la zone processeurs et la zone FPGA permettent des débits élevés pour par exemple des applications de vision ou de télécommunication.

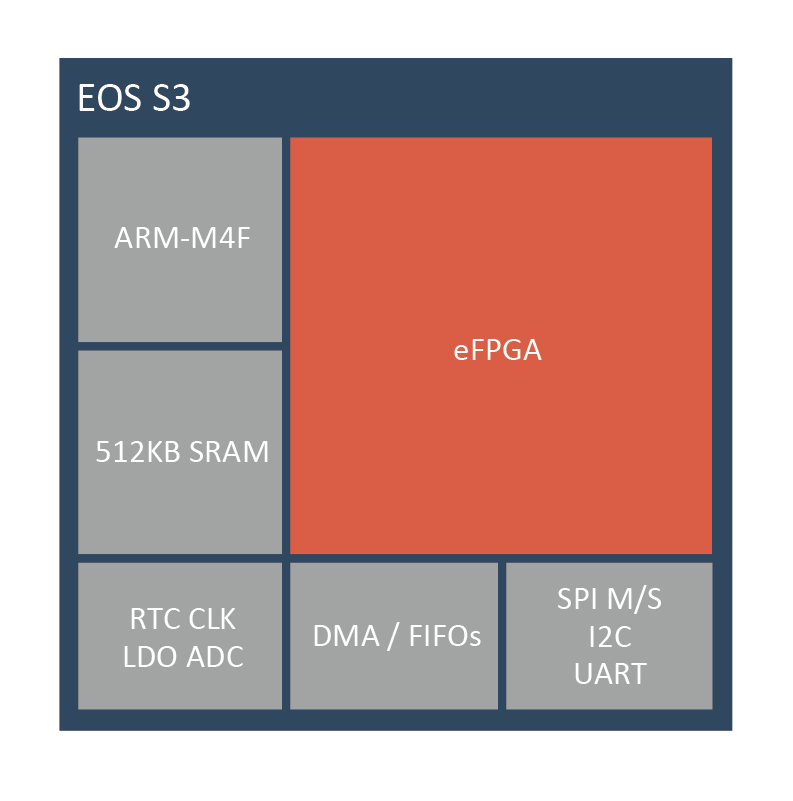

D’autres acteurs proposent des systèmes plus orientés microcontrôleur. Ces fabricants ciblent des applications plus spécifiques liés à la sécurité par exemple ou aux applications basse consommation.

Ici, c’est plus une zone ré configurable (FPGA) à l’intérieur d’un microcontrôleur.

QuickLogic est une des rares entreprises à baser son flot de conception FPGA sur des outils libres.

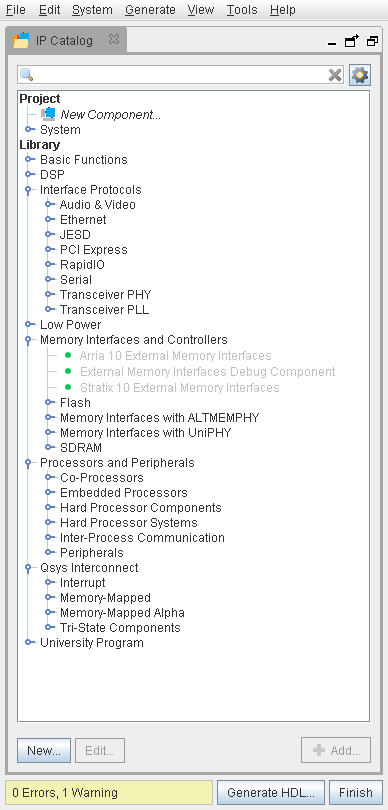

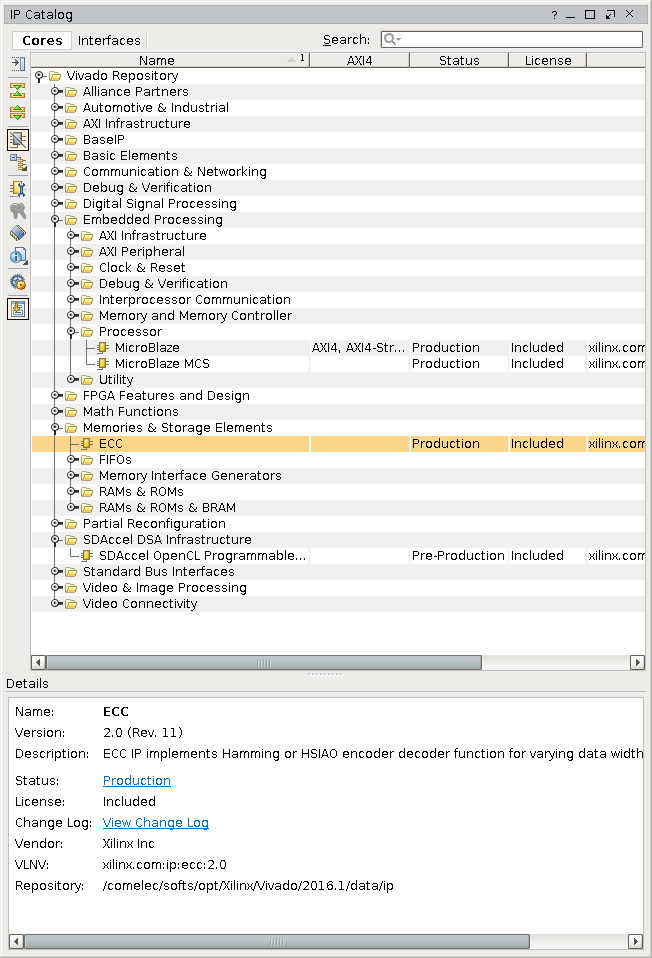

Pour le développement orienté SoC, des outils permettant d’intégrer des IPs sont généralement fournis. Ils permettent de construire la structure de l’interconnect, de définir la carte mémoires et de générer le code RTL. Ces outils fonctionnent généralement de façon similaire pour les systèmes utilisant un softcore ou hardsystems.

Ces outils intègrent aussi de quoi vérifier que les règles d’interconnexion ont été respectées (DRC pour Design Rules Check). Ils permettent ainsi d’éviter d’introduire des erreurs manuellement dans la phase d’interconnexion.

Pour pouvoir ajouter ses propres IPs, les outils proposent généralement des méthodologies plus ou moins similaires ainsi que des assistants permettant d’aider à l’intégration.

Comme le matériel peut changer:

BSP: Board Support PackageIDE: Integrated Development Environment

EclipsePour les développements logiciels, les fabricants de FPGA fournissent des environnements de développement intégrés. Ces IDE sont connectés aux outils d’intégration matérielle et permettent généralement de mettre à jour des fichiers source en fonction de la structure du système qui ici peut évoluer.

Comme pour les IPs matérielle, il est souvent possible d’ajouter ses propres drivers qui seront automatiquement associés au projet logiciel.

| © Copyright 2022-2026, Tarik Graba, Télécom Paris. | |

|

Le contenu de cette page est mis à disposition selon les termes de la Licence Creative Commons Attribution - Partage dans les Mêmes Conditions 4.0 International . |