Un ensemble de composants:

- un processeur généraliste,

- des processeurs dédiés,

- des mémoires,

- des interfaces internes et externes…

Introduction

2025-2026

C’est un système programmable spécialisé construit autour d’un processeur pour accomplir des tâches spécifiques.

Pourquoi spécialiser?

Dans un système embarqué, nous avons toujours un élément programmable, un processeur, qui permet de le personnaliser aux besoins de l’application.

Ce qui différencie un système embarqué d’un système informatique générique (par exemple un ordinateur personnel ou un serveur) est le fait qu’il est conçu pour une tâche spécifique et que le logiciel qu’il embarque est rarement modifiable par l’utilisateur final.

Souvent les composantes matérielle et logicielle sont conçues conjointement. Ceci permet de réduire les coûts de production et de garantir que les performances (vitesse, temps réel, consommation) sont respectées.

Comme les tâches prévues pour le système sont prédéfinies, il est possible d’optimiser son architecture pour répondre aux contraintes de coût et de performance. Pour cela, des éléments dédiés sont inclus. Par exemple:

Un ensemble de composants:

Cet exemple montre la carte mère d’une console de jeu de la fin des années 1990. Plusieurs composants sont visibles dont les principaux sont:

Un ensemble de composants:

Dans cet exemple, nous avons la carte mère d’un smartphone moderne. Nous constatons que le nombre de composants est bien moindre malgré des performances plus élevées comparées à l’exemple précédent.

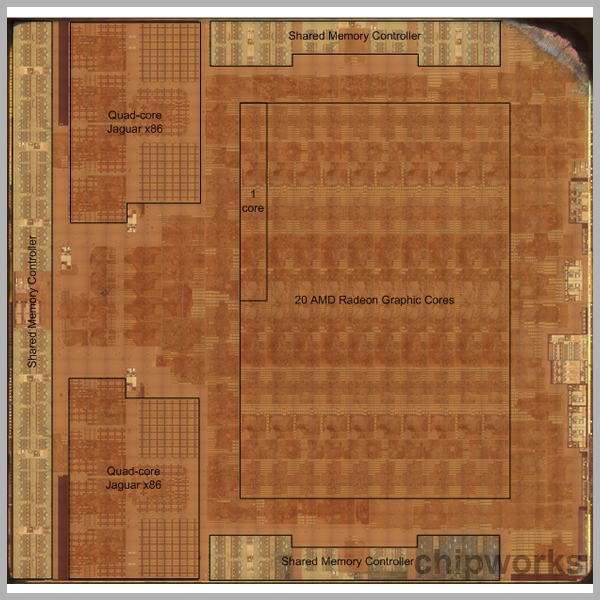

Le composant principal, le SoC, intègre:

Certains éléments ne sont pas encore intégrés su SoC, comme:

Cette intégration plus poussée du système numérique dans la même puce permet de réduire les coûts de fabrication du système embarqué.

C’est un système programmable intégré et spécialisé construit autour d’un processeur pour accomplir des tâches spécifiques.

Les éléments intégrés dans un système sur puce vont dépendre de l’application visée (téléphonie mobile, automobile, IoT…).

Ils doivent permettre de répondre aux besoins dans les limites de coûts liées au marché visé.

Un intégrateur préfèrera payer un composant un peu plus cher s’il lui fait économiser sur la fabrication du PCB et l’intégration dans le produit final.

Le terme ASIC (Application Specific Integrated Circuit), bien que plus générique, peut aussi être utilisé.

Un peu partout:

Compte tenu de la nature des applications cibles, les systèmes sur puces conçus pour ces différentes applications seront très différents:

Exemple, les SoC pour la téléphonie mobile:

Texas Instruments (Ti) leader du marché de la téléphonie mobile au début des années 2000. La plateforme OMAP était destinée au marché naissant des smartphones.

TI n’a pas développé à temps de SoC avec un MODEM 3G/4G intégré. Le marché a été pris par les concurrents et la division OMAP a été arrêtée.

Très rapidement, l’intégration des MODEMs dans les SoC destinés à la téléphonie mobile est devenue la norme. Surtout dans les composants destinés aux smartphones d’entrée/milieu de gamme comme ici un SoC Mediatek de 2015.

Ceci fait apparaitre une contrainte forte des SoC modernes, le temps de développement (time to market). Il est en effet essentiel de fournir un certain nombre de fonctionnalités, considérées comme nécessaires, avant même de pouvoir se différentier de ses concurrents.

Cette contrainte a entrainé la mutualisation de certains développements entre les acteurs du marché pour faciliter la réutilisation de certains blocs matériels.

Ce système sur puce produit par NXP est destiné aux applications automobiles (voiture intelligente) et industrielles. Il intègre des éléments lui permettant de gérer des flux d’images et de la vidéo ainsi que d’implémenter des algorithmes de reconnaissance.

Son architecture diffère de celle des SoC dédiés aux applications de téléphonie par:

Si on regarde l’architecture interne d’un microcontrôleur moderne, nous avons bien un Système sur puce. Les applications ciblées par ce type de composants seront fortement contraintes par le coût et la consommation énergétique.

Certains SoC (ici un microcontrôleur 8-bits) peuvent intégrer des composantes analogiques (ici une interface radio).

L’intégration de parties analogiques dans un SoC est souvent réservée à certaines familles de produits et nécessite des procédés de fabrication ad hoc.

Finalement, certaines familles de FPGA (par exemple les Zynq de Xilinx) intègrent des systèmes sur puce complets reliés à la patrie FPGA.

La partie configurable permettant de s’adapter à l’application tout en profitant de l’environnement logiciel standard lié à la partie processeur.

La majorité des processeurs modernes sont en fait des SoC.

Par exemple, ici la figure montre l’architecture interne d’un processeur core-i7 d’Intel. Il intègre plusieurs cœurs de processeur, un processeur graphique plus de quoi gérer des interfaces avec le monde extérieur.

Bien que ce processeur ne soit pas destiné à un usage spécifique, l’intégration des différents éléments dans la même puce permet de garantir les performances et de baisser le coût de fabrication des cartes mère de PC.

Les circuits numériques programmables modernes, sont tous plus ou moins des SoC. Ce qui va les différentier, c’est les contraintes liées à leur utilisation.

| schéma | physique | |

|---|---|---|

Le composant de base dans les systèmes électroniques est le transistor. Plus particulièrement, pour les circuits numériques le transistor à effet de champs métal/oxyde/silicium (MOS).

La figure précédente montre le schéma usuel d’un transistor nMOS. Jusqu’à ces dernières années, un transistor, pour des applications numériques, était réalisé de façon planaire.

Comme le montre la figure de droite, le transistor est un objet physique avec des dimensions. Sur un substrat de silicium (en jaune), nous avons deux diffusions de dopant (en gris) créant le drain et la source. La grille conductrice (en rouge) est isolée du substrat par une couche d’oxyde de silicium (en bleu).

| symbole | schéma | physique | ||

|---|---|---|---|---|

La construction de porte logique se fait en logique CMOS. Deux types transistors à commandes complémentaires, nMOS et pMOS, sont utilisés. Ceci garanti qu’en régime statique (si les entrées ne bougent pas) il n’y a quasiment pas de consommation électrique.

Ces dessins correspondent aux différentes étapes de fabrication des circuits. Ils vont décrire la position et la taille des différents éléments constituants les portes logiques. La position des diffusions des transistors, les grilles, les connexions.

Pour les circuits numériques, les concepteurs utilisent des bibliothèques de cellules standards. Elles sont assemblées par aboutement pour constituer le layout du circuit à partir d’une netilst par les outils de CAO.

Le dessin complet des masques du circuit sera utilisé pour la fabrication. Le nombre de masques et leur signification dépend du fabricant. Le format GDSII est le standard utilisé par l’industrie pour représenter ces masques.

Ces dessins permettent la fabrication de masques qui seront utilisés dans les étapes de photo-lithographie de la fabrication.

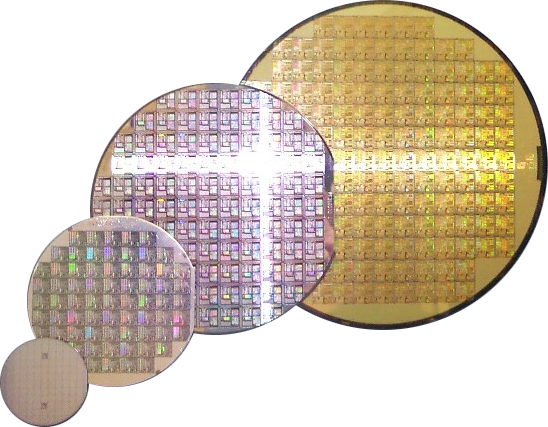

Les wafers (ou galettes, tranches) sont des disques de silicium sur lesquels les circuits sont fabriqués. Pour une production industrielle, le même circuit est dupliqué plusieurs fois dans le même wafer. Pour les fonderies avancées, les wafer font généralement 30 cm de diamètre (12 pouces).

Dans le coût de fabrication d’un cicuit, deux éléments importants:

Pour le même nœud technologique, le coût final du circuit va quasiment exclusivement être lié à sa surface (combien de circuits fonctionnels par wafer).

Après fabrication, il restera à :

Pour un transistor MOS planaire:

L (distance entre le drain en

la source),W,sont les paramètres qui vont influer sur sa performance.

Pour les applications numériques, il est important d’avoir le transistor le plus petit qui fonctionne suffisamment bien comme interrupteur.

Pour un nœud technologique donné, les fabricants définissent les dimensions minimales d’un transistor. Les fabricants vont référencer ce nœud technologique par rapport à la longueur minimale de grille.

I_{0} \approx K_n\cdot(V_{dd}-V_{tn})^2

t_{p} = C_{par}\frac{\Delta V}{I_{0}} = C_{par}\frac{V_{dd}}{K_n\cdot(V_{dd}-V_{tn})^2}

Le temps de propagation dans une porte CMOS est lié à la vitesse à laquelle les transistors de la porte parviennent à charger (pour passer de 0 à 1) ou décharger (passer de 1 à 0) les capacité de ce qui les suit (les grilles des portes suivantes et les capacités des lignes de routage).

Ce temps va dépendre de la tension d’alimentation, du type de transistor et de ses dimensions.

Dans la formule précédente, K_n = \frac{1}{2} \mu_{0N}\cdot C'_{ox} \frac{W_{N}}{L_{N}}, avec:

E = \int_0^{V_{dd}} C_{par} V_{S} dV_S = \frac{1}{2} C_{par} V_{dd}^2

P = \alpha\cdot C\cdot f\cdot V_{dd}^2

Une porte CMOS ne consomme qu’au moment des transitions. L’alimentation va fournir une énergie C_{par} V_{dd}^2 qui sera dissipée dans le circuit.

Un circuit fonctionnant à une fréquence f avec un taux d’activité (la proportion des portes qui changent d’état à chaque cycle) dissipera donc une puissance \alpha\cdot C\cdot f\cdot V_{dd}^2.

Aussi, comme les transistors ne sont pas des interrupteurs parfaits, il existe aussi une consommation statique qui, pour les technologies récentes, n’est pas négligeable.

Pour un nœud technologique:

complexité \rightarrow nombre de transistors \rightarrow coût

La loi de Moore, est une loi auto-prédictive. Pour attendre les objectifs de doublement des densités d’intégration, les fabricants de semi-conducteurs développent en mettent en œuvre les techniques permettant de les atteindre.

Bien qu’on ait prédit, depuis plusieurs années maintenant, la fin de la loi de Moore, la densité d’intégration continue d’augmenter régulièrement. Les investissements nécessaires pour atteindre ces objectifs sont de plus en plus couteux ce qui a conduit à une concentration des acteurs de l’industrie microélectronique. Actuellement seuls trois entreprises dans le monde sont capables de produire des circuits dans les technologies les plus avancées (en deçà de 10 nm):

Pour les technologies planaires, en passant à un nœud \beta plus petit on essaye de:

On obtient pour les performances:

L’amélioration de ces paramètres, permise par le changement d’échelle dû au passage à un nœud technologique plus petit, permet de:

En gardant la même fonctionnalité et donc le même nombre de transistors et la même fréquence de fonctionnement, nous avons un circuit plus petit (1/\beta^2) donc moins cher à fabriquer. Aussi, comme l’énergie de transition est plus faible et que la fréquence reste la même on aura une puissance dissipée plus petite (1/\beta^3).

Ceci permet d’envisager de faire fonctionner des applications, qui avant nécessitaient des systèmes onéreux et énergivores, sur des systèmes mobiles (fonctionnant sur batterie) peu couteux, juste en profitant de l’avancée des technologies de fabrication.

Pour le même coût (donc surface), nous pouvons augmenter le nombre de transistors (\times \beta^2) et donc la complexité du circuit. Nous pouvons aussi augmenter la fréquence de fonctionnement (\times \beta). La puissance consommée reste dans ce cas la même.

Ceci permet d’offrir, pour le même coût et avec le même budget énergétique, plus de fonctionnalité. C’est comme ceci qu’on se retrouve avec des processeurs (de serveurs, PC ou smartphones) qui sont de plus en plus puissants.

Cet extrait du rapport annuel d’activité de TSMC donne une idée de l’évolution de la densité d’intégration pour les nœuds avancés. Par rapport au nœud 55 nm, pour la même complexité (nombre de transistors), un circuit sera 96,5% plus petit en utilisant le nœud 5 nm.

Il faut aussi noter que TSMC conserve en activité des usines (FABs) pour d’anciens nœuds.

Tous les produits n’ont pas besoin des derniers nœuds technologiques.

Le coût d’accès aux nœuds avancés est très élevé, les réservant à des marchés avec de grands volumes et de fortes marges (Smartphones, processeurs de PC/serveurs, cartes graphiques…)

Maintenir d’anciens nœuds éprouvés est

Cette figure est extraite du même rapport d’activité. Elle montre deux choses importantes:

Les circuits qui utilisent les nœuds avancés, ont tendance à augmenter leur complexité d’une génération à l’autre. La réduction de consommation, permise par l’avancée technologique, permet alors de conserver une consommation stable.

// 60 frames/s display

Thread1 {

every(16.66ms)

display(image)

}

// scene update

Thread2 {

if(ViewChanged)

redraw(image)

}

// player interaction

Thread3 {

wait(player1)

move(rabbit0)

}

Comment passer d’une fonctionnalité (algorithme) à un circuit?

À partir d’un cahier des charges de l’application, définir:

Le support logiciel dans un SoC est une composante importante qu’il ne faut pas négliger. Il est important de prévoir la possibilité de configurer, corriger, utiliser ou faire utiliser le produit après la fabrication du circuit.

À l’opposé d’un circuit programmable générique, qui doit anticiper proposer des fonctionnalités qui pour des applications non connues à l’avance, pour un SoC destiné à une application spécifique, l’étape de partitionnement est très importante.

À partir du cahier des charges, on doit identifier les fonctionnalités qui peuvent être implémentées de façon logicielle et évaluer les performances nécessaires pour une cible processeur. Si cela est compatible avec les objectifs de coût et de consommation en utilisant des cibles existantes, il n’est peut-être pas utile de développer un matériel dédié.

Sinon, il faut décider quelles fonctionnalités auront besoin d’une implémentation matérielle et comment partager les tâches.

En plus du cahier des charges de l’application, d’autres éléments vont intervenir dans le choix du partitionnement.

D’un point de vue logiciel, l’existence (et la disponibilité) de bibliothèques logicielles, de systèmes d’exploration (ainsi que de pilotes) doit être considérée.

D’un point de vue matériel, les blocs matériels existant doivent être pris en compte.

Au-delà de l’existant, il faudra prévoir d’éventuelles adaptations à l’application développée ainsi que les développements spécifiques nouveaux.

Il faut aussi prendre en compte les fonctions annexes qui devront être fournies par le système.

Des blocs matériels réutilisable!

Le pendant matériel des bibliothèques logicielles.

Indépendamment de la licence de distribution de l’IP (libre ou non), elle peut être distribuée sous la forme de:

L’utilisation d’IPs physiques permet de garantir, à priori, un certain niveau de performances et de fonctionnalité. La majorité des blocs analogiques, ou nécessitant un dimensionnement ou un placement/routage particulier sont distribuées sous cette forme.

Par exemple:

Certains blocs numériques, nécessitant un effort de placement routage important, sont aussi distribués sous cette forme. Comme, par exemple des cœurs de processeurs complexes avec leurs mémoires cache.

Les IPs physiques sont aussi souvent accompagnées de modèles pour la simulation qui permettent quand même de simuler le système dans sa globalité.

Il faudra prévoir des iterrations de test et de validation:

Dans un flot de conception conjoint, au-delà des cycles de développement et validation des fonctions logicielles et matérielles, il faudra mettre en place des mécanismes de validation conjointe. Il ne s’agit pas seulement de vérifier que le logiciel fonctionne avec le matériel, mais aussi de garantir que les performances prévues sont bien présentes (vitesse, consommation, coût). Si les performances ne sont pas atteintes, il faudra, éventuellement, revenir sur le partitionnement initial.

Il est important de noter que, du fait du coût important de la fabrication d’un circuit, ces étapes de validation doivent avoir lieu en amont.

Il est souvent complexe d’avoir un référentiel commun pour la validation:

Il est important de conserver une référence, commune aux différentes équipes impliquées, tout au long des phases de développement.

Cette référence peut être:

La mise en place d’une telle référence est un enjeu important dans la conception de SoC complexes.

Les échelles de temps ne sont pas les mêmes.

Attendre la fabrication d’un circuit pour tester le logiciel dessus, n’est pas raisonnable!

Une fois l’architecture matérielle définie, il faudra développer un modèle fonctionnel intégrant les différentes IPs (ou des modèles comportementaux). Ceci permet de vérifier que les spécifications sont respectées.

Ensuite, les modèles sont raffinés vers des modèles RTL synthètisables. Une fois ces modèles validés, on passe dans une deuxième phase du flot de conception appelée backend.

Durant cette phase, les étapes de synthèse et de placement routage ont lieu ainsi qu’une série d’étapes de validation pour arriver finalement aux dessins des masques.

Tout au long des phases de développement conjoint (matériel/logiciel), des mécanismes de vérification sont mis en place:

La filière microélectronique est organisée en strates de spécialisations allant de la conception et la fabrication d’un circuit intégré.

Cette pyramide, montre que la filière est organisée de telle façon que le nombre d’acteurs impliqués dans chaque étape est de moins en moins important plus va vers les étapes de fabrications.

Certaines entreprises vont être hyper-specialisées et n’intervenir que dans une de ces étapes alors que d’autres vont apparaitre à plusieurs nivaux bien qu’en interne les équipes soient différentes.

Au-delà de la fabrication des circuits intégrés, d’autres acteurs vont intervenir pour la conception et la fabrication des systèmes embarqués dans les produits finaux.

TSMC, Samsung, (Intel)

UMC, SMIC, (ST), GlobalFoundrie, (Micron)…

Ce sont les entreprises qui fabriquent les circuits pour «les autres».

Du fait des investissements nécessaires pour les nœuds avancés, il y a une forte concentration ces dernières années. Il ne reste en effet que trois acteurs (TSMC, Samsung, Intel) ayant des capacités de fabrication pour les nœuds en deçà de 20 nm.

Malgré cela, il existe un marché pour des nœuds moins avancés ou des technologies spécialisées. En Europe, ST, GlobalFoundrie et Micron (pour les mémoires) restent actives et des entreprises continuent à exploiter d’anciennes Fab en ciblant des applications spécifiques (analogique, capteurs, mems). Par exemple, Xfab, continue d’exploiter une Fab 130 nm à Corbeil-Essonnes en France pour des applications analogiques et mixtes.

Note: Les fonderies d’Intel ne sont pas «ouvertes», elles ne fabriquent que des circuits pour Intel. C’est aussi le cas pour des entreprises comme ST ou Micron.

Certaines entreprises qui fabriquent des circuits possèdent leurs propres fonderies. C’est souvent le cas pour les entreprises spécialisées dans la fabrication de mémoires (DRAM, Flash…) car ces composants nécessitent des technologies particulières qui ne sont pas forcément disponibles chez les autres fondeurs. Ici on retrouve, entre autres, Samsung Electronics, Micron ou Kioxia.

Mais, certains fabricants de processeurs généraliste, microcontrôleurs ou SoCs possèdent aussi des Fabs. Le meilleur exemple étant Intel, ces usines sont exclusivement réservées à ces produits. Samsung Electronics, utilise ses Fabs pour ces propres produits, comme la gamme de SoCs Exynos, mais ses Fabs sont ouvertes pour d’autres acteurs. STMicroelectronics, possède aussi un certain nombre d’usines pour les microcontrôleurs et autre capteurs intégrés dont elle est spécialiste.

Ces entreprises, bien que très visibles, ne possèdent pas de fonderies. Elles sous-traitent donc la fabrication des puces à des fondeurs. On parle d’entreprise Fabless.

En fonction du nœud technologique visé, elles pourront mettre en concurrence les différents fondeurs et ainsi adapter leur production aux demandes du marché.

Il faut noter ici, que certaines entreprises comme STM ou Intel vont aussi passer par les services de fonderies externes quand leur capacité de production interne n’est pas suffisante ou n’est pas adaptée. C’est par exemple le cas avec la division FPGA d’Intel (historiquement Altera) qui continue de fabriquer une partie de ses circuits chez TSMC.

Dans cette catégorie, se trouvent beaucoup de petits acteurs qui arrivent à trouver un équilibre financier entre coût de fabrication et revenus.

Ces entreprises sont spécialisées dans les équipements pour les Fabs. Parmi ces équipements, les systèmes de lithographie avancés sont les plus importants et les plus complexes à concevoir.

ASML, historiquement une division de Philips, est devenue l’unique fournisseur des équipements de lithographie pour les nœuds avancés (EUV: Extreme UltraViolet lithography).

D’autres entreprises sont spécialisées dans la production d’équipements entrant dans le processus de fabrication des semi-conducteurs, par exemple:

Ces entreprises, bien que peu connues, jouent un rôle important dans l’écosystème de l’industrie des semi-conducteurs.

Des entreprises spécialisées dans la fourniture de matériaux pour la fabrication.

On peut citer comme exemples (en Frace): - SOITEC - Air liquide

Ces entreprises fournissent les matériaux nécessaires au processus de fabrication, les wafers de silicium, les fluides, les produit photo-sensibles…

Il y a une forte concentration des vendeurs d’outils de CAO pour la microelectronique. Ces entreprises fournissent les outils necessaires pour:

Ces entreprises ont un quasi-monopole et il est souvent indispensable d’utiliser leurs outils pour accéder aux fonderies commerciales.

Il existe malgré tout des tentatives pour proposer un ensemble d’outils libres comme le projet OpenRoad par exemple.

Il est néanmoins toujours pas possible d’avoir un flot ouvert complet sans la participation des fonderies.

Cette étape est celle où intervient le plus d’acteurs.

Certaines entreprises sont spécialisées dans la conception et vont avoir un portfolio d’IPs important.

Ici, nous pouvons citer comme exemples,

À côté de ces spécialistes, les vendeurs d’outils de CAO sont aussi un acteur important dans la conception d’IPs. Ces entreprises ont un large catalogue d’IPs allant des interfaces physiques (usb, pci…), convertisseurs, contrôleurs de communication… Elles profitent du fait qu’elles ont un quasi-monopole sur les outils de développement pour fournir des IPs prêtes à l’emploi.

Aussi, c’est ici que nous trouveront beaucoup de petites et moyenne entreprises (ou start-up). En effet, les investissements financiers restent raisonnables ce qui permet à des entreprises de petites tailles de proposer des produits innovants ou dans des niches délaissées par les plus grands acteurs.

| © Copyright 2022-2026, Tarik Graba, Télécom Paris. | |

|

Le contenu de cette page est mis à disposition selon les termes de la Licence Creative Commons Attribution - Partage dans les Mêmes Conditions 4.0 International . |