Die approbierte Originalversion dieser Dissertation ist an der Hauptbibliothek der Technischen Universität Wien (5. OG) aufgestellt und zugänglich (http://www.ub.tuwien.ac.at).

The approved original version of this thesis is available at the main library of the Vienna University of Technology (5<sup>th</sup> floor) on the open access shelves (http://www.ub.tuwien.ac.at/englweb/).

#### DISSERTATION

# Compiler Backend Generation from Structural Processor Models

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften unter der Leitung von

Ao.Univ.Prof. Dipl-Ing. Dr. Andreas Krall Inst.-Nr. E185 Institut für Computersprachen

eingereicht an der Technischen Universität Wien Fakultät für Informatik

von

Dipl.-Ing. Florian Brandner Matr.-Nr. 9925151 Wilhelmstrasse 45/8 1120 Wien

## Acknowledgments

I would like to thank my advisor Andreas Krall, who not only supervised me during the work on this thesis, but also mentored me during my studies and my diploma thesis. I also thank the staff at the Institute of Computer Languages. In particular, Jens Knoop, for his support, enthusiasm, and for sharing his excellent international connections. My office mates, Dietmar Ebner, Adrian Prantl, and Christian Thalinger for all the insights and discussions, but foremost for the great fun; the research partners from OnDemand Microelectronics, in particular, Karl Neumann; the students Andreas Fellnhofer and David Riegler for their contributions during their masters theses. Martin Schöberl for diverting my attention and widening my personal as well as research scope.

Mum, Alex, Peter, Liese, Bine, and Cathi that showed me how much one can achieve, if the family is on one's side. My great love Nina for pushing and supporting me, and for just about everything else too.

## Kurzfassung

In den letzten Jahren konnte im Bereich der eingebetteten Computersysteme eine rasante Entwicklung beobachtet werden. Prozessoren, die in diesen Systemen eingesetzt werden, unterliegen seit jeher besonders hohen Anforderungen in Bezug auf den Stromverbrauch, die Chipfläche, die Rechenleistung und die Produktionskosten. Bei der Entwicklung eines neuen Prozessors in diesem Gebiet muß besonderes Augenmerk auf kurze Entwicklungszyklen, sowie hohe Flexibilität bei der Realisierung neuer Technologien gelegt werden. Aus diesem Grund wurden in den letzten Jahren applikationsspezifische Prozessoren immer beliebter, da diese ausreichend Rechenleistung bieten, es aber trotzdem erlauben die gegebenen Einschränkungen, ob nun technischer Natur oder nicht, einzuhalten. Wesentliche Grundvoraussetzungen sind hierbei eine gute Kenntnis des geplanten Einsatzbereichs, sowie geeignete Werkzeuge um alternative Prozessorimplementierungen schnell und einfach erproben zu können.

Ein vielversprechender Ansatz, um Eigenschaften dieser Prozessoren formal zu beschreiben, sind Prozessorbeschreibungssprachen. Basierend auf entsprechenden Prozessorbeschreibungen ist es möglich eine Vielzahl von Werkzeugen abzuleiten. So ist es möglich Softwareentwicklungswerkzeuge und Prozessorsimulatoren bereitzustellen, sowie Abschätzungen des zu erwartenden Stromverbrauchs und der benötigten Chipfläche zu berechnen. Durch die automatische Bereitstellung der entsprechenden Werkzeuge können alternative Prozessorentwürfe und unterschiedliche Befehlserweiterungen eines Prozessors schnell und elegant evaluiert werden. Dies verspricht eine entscheidende Verkürzung der Produktentwicklungszyklen.

In dieser Arbeit wird die neu entwickelte Prozessorbeschreibungssprache \*ADL vorgestellt. Im Gegensatz zu verwandten Systemen wird durch diese Sprache ausschließlich die Struktur der Prozessorimplementierung beschrieben. Der Befehlssatz, obwohl durch die Beschreibung nicht explizit dargestellt, ist ein integrales Grundkonzept der Sprache. Ein Extraktionsverfahren analysiert die Struktur des Prozessors und berechnet daraus eine abstrakte Darstellung der einzelnen Befehle, die durch den Prozessor unterstützt werden. Das abstrakte Modell des Befehlssatzes steht in enger Beziehung zu den zugrundeliegenden Hardwarekomponenten. Die Sprache ist daher in verschiedensten Anwendungsszenarien nutzbar. Im Vergleich zu anderen Prozessorbeschreibungssprachen bietet die \*ADL-Sprache eine Vielzahl nützlicher Erweiterungen, die zu besonders kurzen und intuitiv lesbaren Prozessormodellen führen. Dies umfasst beispielsweise erweiterbare Typen zur Beschreibung von Hardwarekomponenten, die Klassen und Templates der Programmiersprache C++ ähnlich sind.

Die Praxistauglichkeit dieses Ansatzes wird am Beispiel eines Übersetzergenerators untersucht. Hier werden die wesentlichen Komponenten eines Übersetzers aus einer gegebenen ADL-Beschreibung generiert. Dies umfasst im Speziellen die Registerbelegung, die Befehlsanordnung, sowie die Befehlsauswahl. Messungen zeigen,

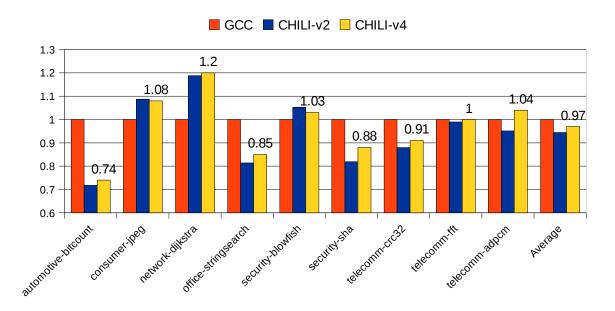

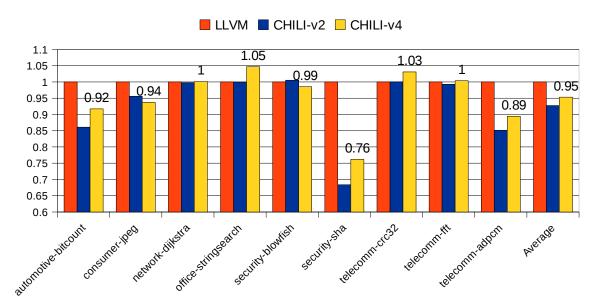

dass die generierten Übersetzer mit handgeschriebenen Produktivsystemen konkurrieren können. Für eine Beschreibung der MIPS-Architektur erzielt der generierte Übersetzer Laufzeitverbesserungen von bis zu 9% für einzelne Benchmarkprogramme. Im Durchschnitt ist eine moderate Verschlechterung der Laufzeit von lediglich 15% festzustellen. In Anbetracht der um bis zu 34% verminderten Codegröße sind diese Ergebnisse ausgezeichnet. Noch bessere Resultate wurden für zwei Konfigurationen des VLIW-Prozessors CHILI erreicht. Hier beträgt die Laufzeitverbesserung bis zu 20%, bei gleichzeitiger Reduktion der Codegröße zwischen 3% und 47%. Im Durchschnitt über alle Benchmarkprogramme ist eine minimale Verschlechterung der Laufzeit messbar, die 5% beziehungsweise 3% beträgt.

Zusätzlich wird die Vollständigkeit der generierten Übersetzer untersucht, d.h., ob der resultierende Übersetzer tatsächlich in der Lage ist für alle durch die Sprache zulässigen Eingabeprogramme entsprechenden Maschinencode zu erzeugen. Traditionelle Ansätze, basierend auf Baumautomaten, sind im Rahmen heutiger Übersetzersysteme nur bedingt einsetzbar, da häufig verwendete dynamische Überprüfungen während der Befehlsauswahl nicht dargestellt werden können. Ein neues Verfahren namens Terminal Splitting wird vorgestellt, das erlaubt diese Überprüfungen explizit durch neue Terminalsymbole darzustellen. Eine durch Terminal Splitting vorverarbeitete Spezifikation der Befehlsauswahl wird sodann mit Hilfe des traditionellen Ansatzes auf Vollständigkeit geprüft. Das vorgeschlagene Verfahren ist vollständig in den Übersetzergenerator integriert und erlaubt dem Prozessordesigner wertvolle Information in der Form von Gegenbeispielen zur Verfügung zu stellen.

## Abstract

The embedded systems computing domain showed a tremendous development in recent years. Processors used in these systems face rigid constraints in terms of power consumption, chip area, performance, and production costs. Short development cycles and great flexibility in the adoption of new technologies are key factors for successful embedded processors. Application-specific instruction set processors have proven successful in providing the necessary computing power, while meeting the various technical and non-technical design constraints. However, the development of such processors requires intimate knowledge of the processor's application domain and appropriate tools to evaluate design alternatives quickly.

A promising approach to formally specify processor design alternatives and automatically derive the necessary tools for design space exploration are processor description languages. These languages capture the instruction set, and often also the hardware organization of the given processor using an abstract specification. The information provided through the processor models can be used to automatically derive software development and simulation tools, as well as area and power estimates. This approach has the potential to significantly reduce the turn-around time during the evaluation phase of a new application-specific processor, because alternative instruction set extensions and hardware designs can be specified and evaluated systematically.

In this work the novel \*ADL language is presented, which, in contrast to most contemporary processor description languages, focuses on a structural modeling of the processor's hardware organization. The instruction set, even though not specified explicitly, is a central concept of the language and its support tools. Through instruction set extraction an abstract model of the instruction set is automatically derived from the structural specification. The instruction set view combined with the detailed hardware model provides the necessary information to derive high-quality tools for design space exploration. The language allows the reuse of hardware components through extensible types, similar to classes and templates known from the C++ programming language. In comparison to other processor description languages, \*ADL specifications are thus very compact and readable.

The feasibility of the approach is demonstrated by a compiler backend generator. It is shown how the essential processor-specific components of a compiler backend can be derived from **\*ADL** models, including the register allocator, the instruction scheduler, and the instruction selector. The automatically generated compilers are competitive to handcrafted production compilers. For a MIPS processor model speedups of up to 9% have been measured for certain benchmarks. On average a moderate slowdown of 15% has been observed, which is remarkable considering the code size reduction of up to 34%. Even better results have been measured for two configurations of the CHILI VLIW processor, where speedups of up to 20% and an

average slowdown of only 5% to 3% can be reported. The code size reductions for the CHILI range from 3% up to 47%.

Further, the completeness of the generated compiler components is investigated, i.e., whether the generated compiler is able to produce machine code for all input programs possibly accepted by the compiler frontend. Traditional approaches based on tree automata are not applicable in the context of modern compilers, instruction selection process is often controlled by dynamic checks. These checks can not be represented by tree automata. Terminal splitting is proposed to explicitly represent the dynamic checks present in the instruction selector specification. The transformed specification is then processed by a traditional completeness test. The proposed approach is integrated with the compiler generator system and thus provides valuable feedback to the processor designer in the form of counter examples.

CONTENTS vi

## Contents

| 1 | Intr | oducti | ion                                       | 1  |

|---|------|--------|-------------------------------------------|----|

|   | 1.1  | Proces | ssor Description Languages                | 3  |

|   |      | 1.1.1  | Behavioral Languages                      | 5  |

|   |      | 1.1.2  | Structural Languages                      | 6  |

|   |      | 1.1.3  | Mixed Languages                           | 6  |

|   |      | 1.1.4  | Architecture Styles                       | 7  |

|   | 1.2  | Applie | cation of Processor Description Languages | 7  |

|   |      | 1.2.1  | Documentation and Design                  | 8  |

|   |      | 1.2.2  | Verification and Validation               | 8  |

|   |      | 1.2.3  | Assembler and Linker                      | 9  |

|   |      | 1.2.4  | Compiler                                  | 9  |

|   |      | 1.2.5  | Instruction Set Simulator                 | 10 |

|   |      | 1.2.6  | Hardware Synthesis                        | 10 |

|   |      | 1.2.7  | Encoding Optimization                     | 10 |

|   | 1.3  | Retarg | getable Compilation                       | 11 |

|   | 1.4  | Scope  | and Contributions                         | 13 |

| 2 | Rel  | ated V | Vork                                      | 17 |

|   | 2.1  | MIMO   | OLA - A Structural Language               | 20 |

|   |      | 2.1.1  | Program Specification                     | 21 |

|   |      | 2.1.2  | Structure Declaration                     | 22 |

|   |      | 2.1.3  | Compiler Generation                       | 23 |

|   | 2.2  | EXPR   | RESSION - A Mixed Language                | 25 |

|   |      | 2.2.1  | Instruction Set View                      | 26 |

|   |      | 2.2.2  | Structural View                           | 26 |

|   |      | 2.2.3  | Compiler Generation                       | 28 |

CONTENTS

| 3 | The | xADL    | Language                | 30       |

|---|-----|---------|-------------------------|----------|

|   | 3.1 | Config  | uration                 | 33       |

|   | 3.2 | Compo   | onent Types             | 33       |

|   |     | 3.2.1   | Immediate Operands      | 34       |

|   |     | 3.2.2   | Register Files          | 34       |

|   |     | 3.2.3   | Storage Elements        | 36       |

|   |     | 3.2.4   | Functional Units        | 38       |

|   | 3.3 | Compo   | onent Instances         | 42       |

|   | 3.4 | Inherit | cance and Generics      | 44       |

|   | 3.5 | Compo   | osing Data Paths        | 46       |

|   |     | 3.5.1   | Data and Pipeline Links | 47       |

|   |     | 3.5.2   | Hazard Links            | 49       |

|   |     | 3.5.3   | Signals                 | 50       |

|   |     | 3.5.4   | Parallel Pipelines      | 51       |

|   |     | 3.5.5   | Restricting Data Paths  | 51       |

|   | 3.6 | Meta-I  | Information             | 53       |

|   |     | 3.6.1   | Assembly Syntax         | 53       |

|   |     | 3.6.2   | Binary Encoding         | 57       |

|   |     | 3.6.3   | Programming Conventions | 61       |

|   | 3.7 | Instruc | ction Set               | 63       |

|   |     | 3.7.1   | Instruction Paths       | 66       |

|   |     | 3.7.2   | Instructions            | 68       |

| 4 | Tho | adlan   | n Tool                  | 70       |

| 4 | 4.1 |         | <i>n</i> 1001<br>nd     | 70<br>71 |

|   | 4.1 |         |                         | 72       |

|   | 4.2 |         | ler                     | 75       |

|   | 4.3 |         | es                      | 79       |

|   | 4.4 | would   | .55                     | - 19     |

CONTENTS viii

82

5 Compiler Backend Generation

| 7 | Con | clusio         | n                                               | 128   |

|---|-----|----------------|-------------------------------------------------|-------|

|   | 6.4 | Comp           | leteness of Instruction Selector Specifications | . 125 |

|   | 6.3 |                | nd Generation for LLVM                          |       |

|   | 6.2 |                | nd Generation for $acc$                         |       |

|   | 6.1 | Proces         | ssor Models                                     | . 113 |

| 6 | Exp | erime          | ntal Results                                    | 113   |

|   |     | 5.6.5          | Final Completeness Test                         | . 111 |

|   |     | 5.6.4          | Chain Rules                                     |       |

|   |     | 5.6.3          | Terminal Splitting                              |       |

|   |     | 5.6.2          | Preliminaries                                   |       |

|   |     | 5.6.1          | Equality Constraints                            |       |

|   | 5.6 | -              | leteness of Instruction Selector Specifications |       |

|   |     | 5.5.6          | Emitting the Instruction Selector Specification | . 105 |

|   |     | 5.5.5          | Specializations and Templates                   | . 103 |

|   |     | 5.5.4          | Initial Rule Set                                | . 100 |

|   |     | 5.5.3          | Deriving Conversion Rules                       | . 99  |

|   |     | 5.5.2          | Deriving Non-terminals                          | . 98  |

|   |     | 5.5.1          | Representing Tree Rules                         | . 96  |

|   | 5.5 | Instru         | ction Selector Specifications                   | . 96  |

|   |     | 5.4.2          | Operation Tables for the <i>acc</i> Backend     |       |

|   |     | 5.4.1          | Resource Tables for the LLVM Compiler           |       |

|   | 5.4 |                | rce Models                                      |       |

|   | 5.3 |                | ction Definitions                               |       |

|   | 5.2 |                | ser Specifications                              |       |

|   |     | 5.1.6          | The acc Backend                                 |       |

|   |     | 5.1.5          | The LLVM Compiler Infrastructure                |       |

|   |     | 5.1.4          | Register Allocation                             |       |

|   |     | 5.1.3          | Instruction Scheduling                          |       |

|   |     | 5.1.1<br>5.1.2 | Instruction Selection                           |       |

|   | 5.1 | O              | round                                           |       |

|   | 5 T | Reales         | round                                           | Q()   |

# List of Figures

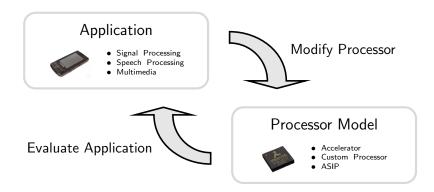

| 1  | The processor model, specified using a processor description language, is iteratively modified during design space exploration in order to achieve the best possible performance, power, and area trade-off for a given application | 2  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

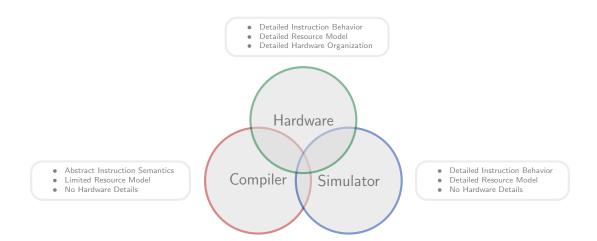

| 2  | Most processor description languages were initially specialized to one particular task, e.g., compiler generation, and were later extended to other tasks                                                                           | 4  |

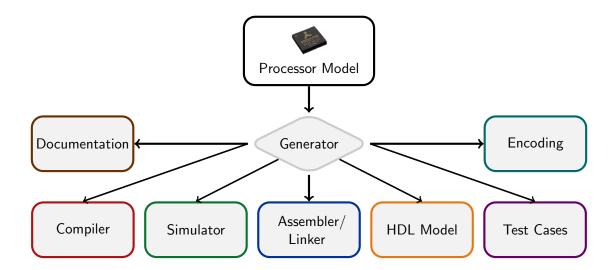

| 3  | Software development tools, test cases and even hardware models in a general purpose hardware description language can be derived from a processor model                                                                            | 8  |

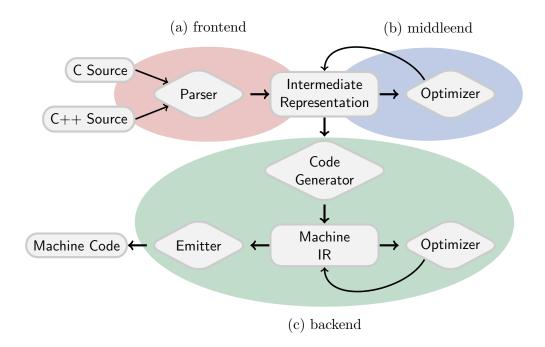

| 4  | Structure of a compiler consisting of (a) a frontend, (b) an optimizing middleend, and (c) an architecture-dependent backend                                                                                                        | 11 |

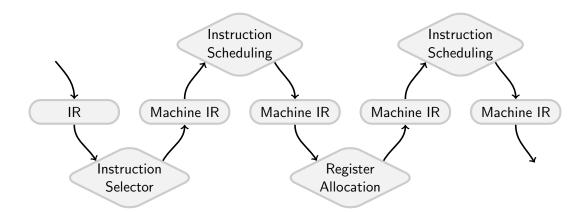

| 5  | The three major phases of a compiler backend, instruction selection, instruction scheduling, and register allocation                                                                                                                | 12 |

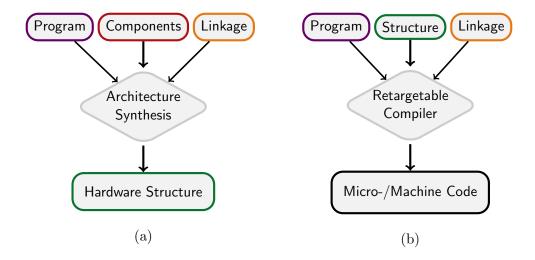

| 6  | Two application scenarios for the MIMOLA system: (a) high-level architecture synthesis, (b) retargetable compilation                                                                                                                | 21 |

| 7  | An example program definition in MIMOLA                                                                                                                                                                                             | 22 |

| 8  | An example module specification in MIMOLA                                                                                                                                                                                           | 23 |

| 9  | An example operation specification in EXPRESSION                                                                                                                                                                                    | 26 |

| 10 | A functional unit specified in EXPRESSION                                                                                                                                                                                           | 27 |

| 11 | An example pipeline description in EXPRESSION                                                                                                                                                                                       | 27 |

| 12 | Compiler specifications in EXPRESSION                                                                                                                                                                                               | 28 |

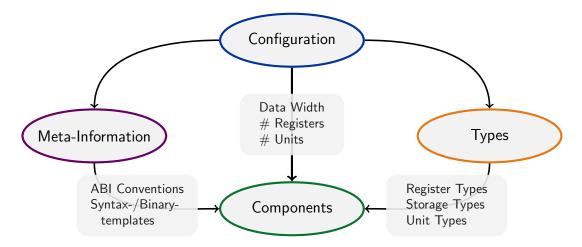

| 13 | The four major sections of a xADL processor model                                                                                                                                                                                   | 32 |

| 14 | Configuration section of the CHILI VLIW core                                                                                                                                                                                        | 33 |

| 15 | Two immediate types of the MIPS model                                                                                                                                                                                               | 34 |

| 16 | Type of the general purpose register file of the MIPS core                                                                                                                                                                          | 34 |

| 17 | Modeling $(1)$ sub-registers and $(2)$ register pairs using register ports                                                                                                                                                          | 35 |

| 18 | The Rx register port is read and then overwritten by the two-address instructions of the SPEAR processor                                                                                                                            | 35 |

| 19 | Concurrent write operations to the same base register are resolved by the order of the register ports for the CHILI model                                                                                                           | 36 |

| 20 | Definition of a memory type of the MIPS processor                                                                                                                                                                                   | 37 |

| 21 | Excerpt of the data cache definition of the CHILI processor                                                       | 38 |

|----|-------------------------------------------------------------------------------------------------------------------|----|

| 22 | Simplified type of the arithmetic unit of the MIPS processor model                                                | 39 |

| 23 | Definition of a constant and a temporary within a functional unit                                                 | 39 |

| 24 | Definition of the add micro-operation                                                                             | 40 |

| 25 | Example operations of the MIPS model                                                                              | 41 |

| 26 | Example of a user-defined micro-operation                                                                         | 42 |

| 27 | Simple instantiation of an immediate type                                                                         | 43 |

| 28 | Register instance of the MIPS model                                                                               | 43 |

| 29 | Memory and data cache instances of the MIPS model                                                                 | 44 |

| 30 | Instantiation of multiple identical units of the CHILI VLIW processor.                                            | 44 |

| 31 | Extending the arithmetic unit of the MIPS model by a DSP multiply-accumulate instruction                          | 45 |

| 32 | Extending a register file of the MIPS processor by an additional accumulator port                                 | 45 |

| 33 | A generic container unit type modeling the MIPS pipeline                                                          | 46 |

| 34 | Instantiating a generic container unit                                                                            | 46 |

| 35 | Unit instantiation including connections to other components                                                      | 47 |

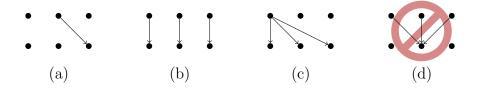

| 36 | Example connection patterns that can be realized using the Connect keyword                                        | 48 |

| 37 | Connect to read from a register file restricted by a modifier                                                     | 49 |

| 38 | A signal aborts the instructions in the decode unit of the MIPS model in case a branch has been taken             | 51 |

| 39 | The addressing modes of the MIPS processor are restricted using predicates and conditions                         | 52 |

| 40 | The addiu operation of the MIPS arithmetic unit defines a predicate to restrict the addressing modes              | 52 |

| 41 | The data cache of the MIPS processor model restricts the valid addressing modes using a condition and a predicate | 53 |

| 42 | Definition of syntax directives and masks of the MIPS processor model.                                            | 54 |

| 43 | A syntax mapping assigns symbolic names to register indices according to the MIPS naming conventions              | 55 |

| 44 | Syntax templates of the SPEAR processor model.                                                                    | 55 |

| 45 | The mnemonic of SPEAR's load immediate low instruction is specified using a syntax binding                                                                                                                        | 56  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 46 | The syntax of operands is specified with the link that connects the operand to the data path                                                                                                                      | 56  |

| 47 | Binary template for the MIPS <i>rtype</i> instruction format                                                                                                                                                      | 57  |

| 48 | Binary mappings specify a space efficient encoding of register operands.                                                                                                                                          | 58  |

| 49 | The binary representation of the <i>add unsigned</i> instruction of the MIPS processor is specified using binary templates                                                                                        | 58  |

| 50 | Final layout of the binary encoding of the MIPS processor                                                                                                                                                         | 59  |

| 51 | Binary encoding using multiple fields                                                                                                                                                                             | 60  |

| 52 | The instruction format defined by a dual-issue processor                                                                                                                                                          | 60  |

| 53 | Programming conventions of the CHILI processor model                                                                                                                                                              | 62  |

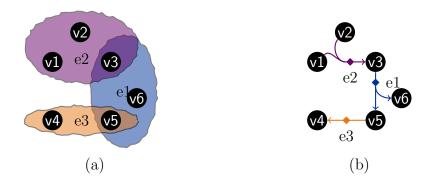

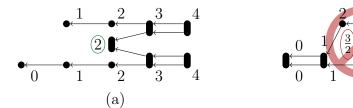

| 54 | Examples of (a) a hypergraph and and (b) a directed hypergraph                                                                                                                                                    | 64  |

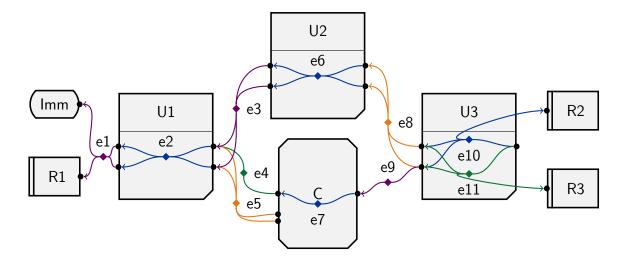

| 55 | Example of a simple data path represented by a directed hypergraph.                                                                                                                                               | 66  |

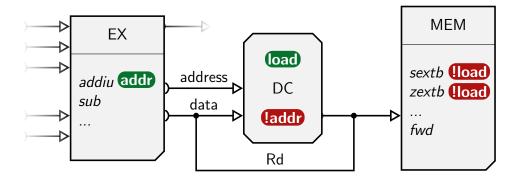

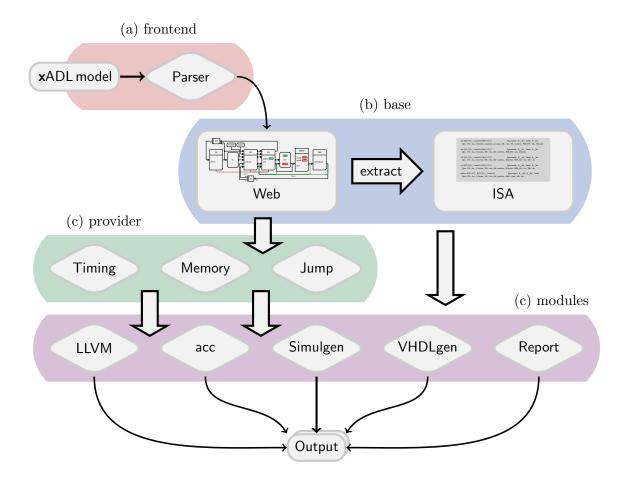

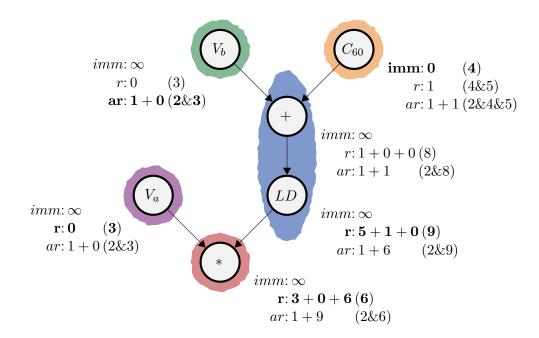

| 56 | Organization of the <i>adlgen</i> tool, (a) the frontend parses the xADL file, (b) base creates an internal representation, (c) provider share common analysis data, and (d) modules generate the final artifacts | 71  |

| 57 | Assignment of pipeline stages to the components and ports of a data path, (a) a legal pipeline structure, (b) an illegal data path organization.                                                                  | 73  |

| 58 | Meta-information associated internally with the <i>or immediate</i> instruction of the MIPS processor                                                                                                             | 74  |

| 59 | Behavioral model of the or immediate instruction                                                                                                                                                                  | 75  |

| 60 | Memory access summary for the MIPS $load\ word$ instruction                                                                                                                                                       | 77  |

| 61 | Branch behavior of two jump and a branch instruction of the MIPS model                                                                                                                                            | 78  |

| 62 | Tree pattern matching using dynamic programming                                                                                                                                                                   | 85  |

| 63 | Register and the register class definitions of the MIPS model for LLVM's register allocator                                                                                                                       | 92  |

| 64 | Example definition of the MIPS jump and link instruction for the LLVM compiler infrastructure                                                                                                                     | 93  |

| 65 | Default rules generated for register and immediate non-terminals                                                                                                                                                  | 99  |

| 66 | Conversion rules derived from overlapping register ports and constant registers.                                                                                                                                  | 100 |

| 67   | Rule patterns derived from the <i>load word</i> and <i>store word</i> instructions of the MIPS model                |

|------|---------------------------------------------------------------------------------------------------------------------|

| 68   | Rule patterns derived from the <i>jump</i> and <i>branch on zero</i> instructions of the MIPS processor             |

| 69   | Micro-operations of the <i>or immediate</i> instruction                                                             |

| 70   | Tree patterns constructed from the micro-operations of MIPS' or immediate instruction                               |

| 71   | Specialization applied to the original rule of the or immediate instruction                                         |

| 72   | Template to match the sign-extend operator                                                                          |

| 73   | Final instruction selection rule for the <i>acc</i> backend                                                         |

| 74   | Final instruction selection rule for the LLVM backend 106                                                           |

| 75   | Example specifications using dynamic checks                                                                         |

| 76   | Terminal splitting for a simple example supporting only 16-bit signed and unsigned constants                        |

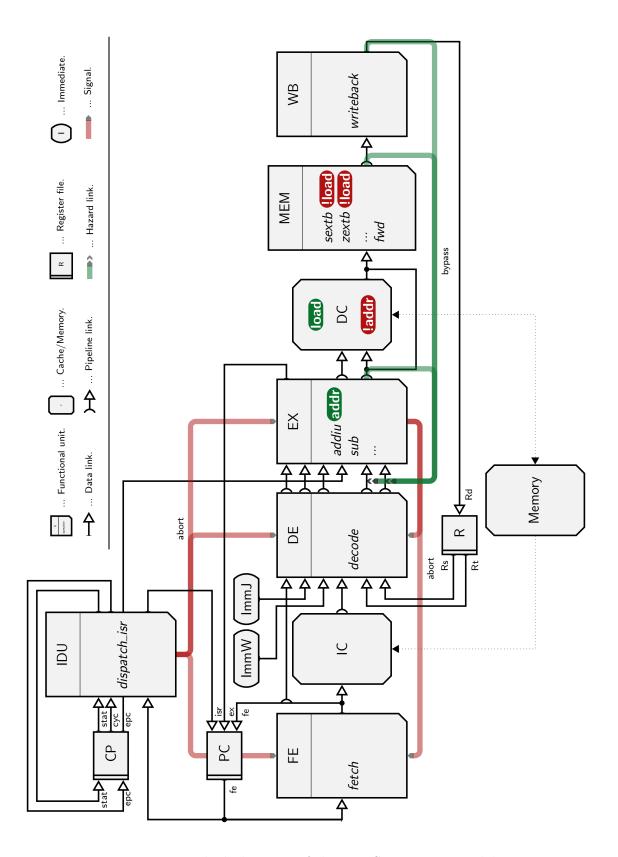

| 77   | Block diagram of the MIPS processor model                                                                           |

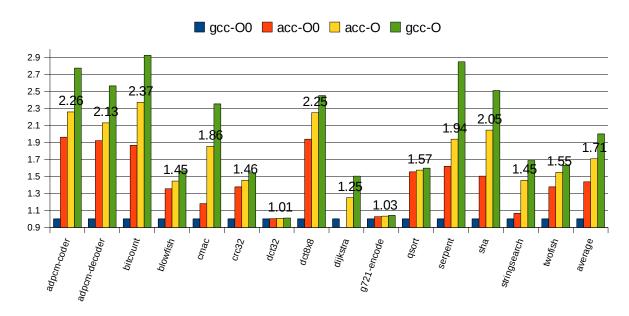

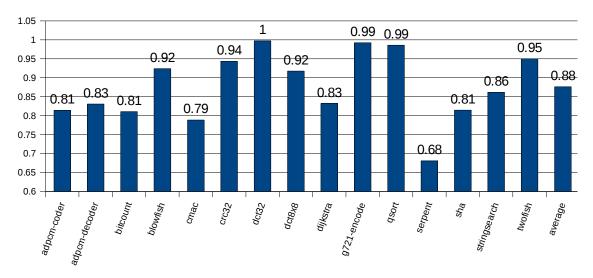

| 78   | Performance improvements of the generated MIPS backend in comparison to the GCC compiler without optimizations      |

| 79   | Performance improvements of the generated MIPS backend in comparison to the GCC compiler with optimizations enabled |

| 80   | Performance difference of the generated backend in comparison to GCC.121                                            |

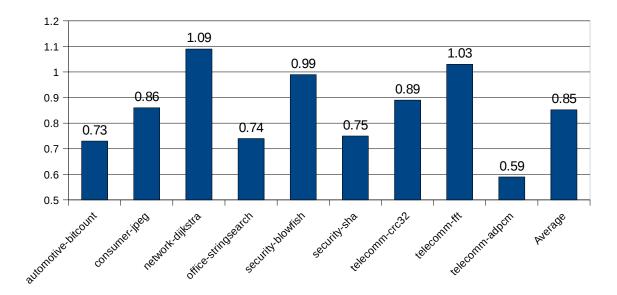

| 81   | Performance improvement of the generated CHILI backends in comparison to GCC                                        |

| 82   | Performance improvement of the generated CHILI backends in comparison to LLVM                                       |

| List | of Tables                                                                                                           |

| 1    | Built-in integer micro-operations available in xADL 40                                                              |

| 2    | Categories to classify register instances                                                                           |

| 3    | Predefined register classes to specify register usage conventions 61                                                |

| 4    | Addressing modes recognized by the memory provider                                                                  |

| 5    | Example tree grammar for instruction selection 84                                                                   |

| 6  | Final machine code generated from a tree cover                                                                                                     |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7  | Operation table of the add unsigned instruction of the MIPS processor. 96                                                                          |

| 8  | Statistics on the MIPS, SPEAR, and CHILI processor models 114                                                                                      |

| 9  | Statistics on the MIPS, SPEAR, and CHILI instruction set models. $$ . $$ 116                                                                       |

| 10 | Statistics on the ArchC MIPS R3000 and acesMIPS EXPRESSION descriptions                                                                            |

| 11 | Size of the benchmark programs in source lines                                                                                                     |

| 12 | Statistics on the generated LLVM backends for the MIPS, SPEAR, and CHILI processor models                                                          |

| 13 | Code size and execution time results for the MIPS processor 120                                                                                    |

| 14 | Code size and execution time results for the two-way parallel CHILI configuration                                                                  |

| 15 | Code size and execution time results for the four-way parallel CHILI configuration                                                                 |

| 16 | Code size and execution time results for the handcrafted LLVM compiler targeting the two-way parallel CHILI configuration                          |

| 17 | Code size and execution time results for the handcrafted LLVM compiler targeting the four-way parallel CHILI configuration                         |

| 18 | Properties of the normalized tree grammars before terminal splitting. 126                                                                          |

| 19 | Number of rules in the tree grammars of the instruction selector and the compiler's IR after the application of chain rules and terminal splitting |

### 1 Introduction

The domain of embedded systems showed a dramatic development during the last years, and today belongs to the largest and fastest growing business in the software and in particular in the semiconductor industry. Embedded systems are almost omnipresent in everybody's life, ranging from mobile phones and personal digital assistants (PDAs), over digital media player for DVDs, blue-ray discs, and MP3s to commodity appliances like refrigerators, coffee machines, and washing machines. Even safety-relevant systems in medical devices, in the automotive industry, and avionics rely on these embedded devices. It is thus not surprising that the field of embedded systems contributes a fair amount to the total sales volume of the semiconductor business, has grown to a driving force in research and innovation, and has become a major field of today's computer science. For example, the sales of processors specialized in *Digital Signal Processing* (DSP) applications, already exceeds 20% of the global semiconductor market since 2002 [120]. Even more, in the year 2006 embedded DSP processors contributed more than 95% of the total volume of processor units sold [120]. The number of general purpose server, workstation, and laptop processors sold in comparison is negligible. Additionally, the market for processors specialized for embedded systems is expected to grow faster than the general purpose computing domain in the foreseeable future, making this field a prominent candidate for future research and innovation.

Embedded processors face a wide range of requirements that differ greatly depending on the particular application domain. The range of applications, however, is very diverse, ranging from general computing tasks and computationally intense multimedia processing in modern mobile phones to computationally less demanding control tasks in the automotive sector that favor predictable and fail-safe behavior over performance. Consequently, specialized processors for different application domains evolved, which are particularly well suited for the functional requirements as well as non-functional requirements, such as performance, power consumption, predictability, robustness, and production costs. This specialization is supported by the very nature of embedded systems: they are usually *invisible* to the end-user, i.e., the end-user is not aware of the computer system involved. The computer is thus only part of a larger system and not in the center of attention. The purpose of the embedded system is usually well-defined and limited in scope. It is thus possible to derive streamlined and optimized solutions for a given task that reduce production costs and increase efficiency.

The ultimate goal of an embedded system engineer is thus not to provide a general computing system, but to derive a specialized system tailored to the functional and non-functional requirements of the problem at hand. In order to achieve this goal, engineers are very flexible in their use of new technologies that are quickly adopted. For example, it is not unusual to change the processor implementations and even vendors frequently during the development of product lines in order to achieve the best efficiency and cost trade-offs. The problem of legacy software and

1 Introduction 2

Figure 1: The processor model, specified using a processor description language, is iteratively modified during design space exploration in order to achieve the best possible performance, power, and area trade-off for a given application.

binary compatibility appears in a relaxed form in embedded systems. The software running on the system is in most cases controlled entirely by the manufacturer and can easily be updated and replaced. Usually, guaranteeing tool compatibility, i.e., compatible tool chains of compiler, linker and assembler, is sufficient in order to rebuild the software for a new platform from source code.

Because of this fast changing and highly competitive environment short development cycles are a key to success. It is thus not surprising that the idea of hard-ware/software co-design has been adopted early in this domain by researchers and engineers alike. Hardware/software co-design is an approach to the development of new systems that tries to achieve optimal results using a balanced mix of hardware and software techniques. The development of the final hardware and software components is tightly coupled and individual tasks are implemented either using flexible software techniques or using efficient hardware solutions as needed. The hardware platform is usually built using a combination of off-the-shelf hardware blocks, customized processors, Application-Specific Instruction Processors (ASIPs), and dedicated hardware accelerators. Very often all these components are integrated on a single chip forming a System-on-Chip (SoC).

Especially, ASIPs are becoming more and more popular in embedded systems. These processing elements are streamlined instruction processors that are particularly well suited for a given target application. A set of special purpose primitives is realized using dedicated instructions that improve the efficiency in terms of power consumption and performance while minimizing silicon area requirements, and thus production costs. At the same time these processing elements still provide enough programmability to adopt the system to new requirements, work around software and hardware bugs or simply update the software stack. However, the development of ASIPs is a highly complex task, that requires intimate knowledge of the application domain as well as hardware and architecture design. In many cases an iterative design process called *Design Space Exploration* (DSE) is used to find an optimal ASIP configuration for a set of typical algorithms of the target application.

Different configurations are evaluated using a preliminary implementation of the algorithms. During this process performance, power and other metrics of interest are collected for each design alternative and stored in a database for later assessment.

Design space exploration opens a large variety of interesting research questions. A major research question is how to minimize the number of design alternatives considered for evaluation in a virtually unbounded design space. Similarly, how can be assured that the most relevant design points are captured during exploration. This work, however, focuses on more fundamental problems, namely: (1) how can design alternatives be modeled formally in a domain specific language, (2) how can the required software tools for the exploration be derived from such a model. *Processor* Description Languages (PDLs) are a promising approach to solve both problems. These languages provide the required primitives to specify the instruction set of a processor design and (semi-)automatically derive software development tools such as compiler, assembler, linker, and instruction set simulator from a given processor model. Figure 1 depicts an example workflow for the design of a new ASIP using a processor description language. The designer iteratively extends and adopts the processor model in order to reach the best possible solution. During each iteration step, a series of simulation runs is performed to evaluate the modifications and expose bottlenecks that have to be dealt with during the next iteration.

### 1.1 Processor Description Languages

In recent years, processor description languages have managed to evolve from being sole research projects into products that are actively used and adopted successfully by leading companies in order to develop and design highly specialized and tuned architectures [76]. A processor model typically consists of several layers that include information on the hardware organization, the instruction set, instruction semantics and timing. Meta-information such as assembly syntax, *Application Binary Interface* (ABI) conventions, etc., can be specified in most languages. Structuring the models, for example by instruction classes, enables code reuse across different instructions and leads to concise and compact models. Thus, adding new instructions or adopting existing instructions is often only a matter of a few lines of code.

Processor description languages, sometimes also referred to as *Architecture Description Languages* (ADLs), can roughly be categorized into three distinct groups [131]:

- 1. **Structural** languages offer primitives that directly match abstractions typically found in *Hardware Description Languages* (HDLs). The processor model thus closely resembles the structure of the actual hardware implementation.

- 2. **Behavioral** languages on the other hand primarily focus on the *Instruction Set Architecture* (ISA), and typically provide some means to structure and order instruction variants and meta-information such as assembly syntax, binary encoding, and abstract instruction semantics.

Figure 2: Most processor description languages were initially specialized to one particular task, e.g., compiler generation, and were later extended to other tasks.

3. **Mixed** approaches finally combine the structural and behavioral view of the processor and provide mechanisms to model both, the hardware structure and the instruction set architecture. A mapping mechanism between the structural and the behavioral description allows to relate information of the two models to each other.

The information that is available in these processor specifications can be used to (semi-)automatically generate software tools that are customized for the particular processor. This includes standard development tools such as a compiler, an assembler, a linker, and an instruction set simulator. However the models can also be used to generate test cases for compiler and hardware verification, can serve as references during hardware development, and can even be used to derive hardware models in a general purpose hardware description language, such as VHDL or Verilog.

The various flavors of languages are usually geared towards a particular application. Figure 2 presents three major application fields and the required information that needs to be available within processor descriptions: (1) compiler generation, (2) generation of instruction set simulators, and (3) hardware synthesis using a general purpose HDL. Compiler generation requires an abstract model of the behavior of the individual instructions in order to map the architecture-independent intermediate representation of the compiler to machine code of the target processor. In addition, a resource model is needed to avoid hazards and ensure correct code. Detailed information on the hardware structure is of less importance for the compiler, i.e., it is not important how the individual instructions are realized in hardware. The situation changes when an instruction set simulation engine is to be generated from a processor model. A detailed model of the instruction behavior is required, along with a detailed resource model that is able to accurately capture all sorts of hazards, stalls, delays, and instruction latencies. The hardware structure is only relevant if the behavior of instructions is influenced, all other details are ignored for the sake

of simulation efficiency. However, this changes when synthesizable hardware models are to be extracted from processor descriptions. For this scenario not only detailed knowledge of the instruction behavior is required, but also details on the timing, the realization in hardware, and the interaction with other hardware components.

Behavioral languages typically support the generation of compiler backends and related development tools, such as assemblers and linkers, very well, but lack information needed for accurate simulation and automatic generation of hardware models. Structural languages are usually well suited for these *low-level* tasks, but in turn lack abstract semantic models of instructions. Generating a compiler is thus more complicated in these systems. To overcome such limitations, many systems have gradually adopted features and ideas from the respective other style. Most contemporary languages thus follow the mixed approach that supports both low-level and high-level applications equally well.

#### 1.1.1 Behavioral Languages

Many languages that follow the behavioral approach originated from generalized compiler backend specification languages. The specifications provide an abstract model of the target processor and focus on the instruction set architecture rather than on implementation details. Consequently, behavioral languages are well suited for high-level tasks such as compiler generation or verification.

The behavior of each instruction is specified separately and annotated with additional properties. These properties usually include the assembly syntax, the binary encoding, and the timing. The instruction specifications often contain redundant information, e.g., instructions that share the same or very similarly structured binary encoding. Many behavioral languages thus allow the reuse of instruction specifications. For example, in nML [57] instructions are specified using a grammar. Derivations of this grammar represent the individual instructions of the target processor. New instructions can be composed using AND-rules that combine several possible partial instruction specifications, and OR-rules that can be used to enumerate variations of an instruction.

Behavioral models do not specify the underlaying hardware organization or structure, except for an abstract model of the registers, memories, and caches. However, constraints of the hardware implementation need to be considered for a faithful model. Many languages thus provide a very basic resource model that is powerful enough to express certain hardware constraints using symbolic resources, very much like resource tables used during instruction scheduling in modern compilers [140].

In addition to the instruction specifications, meta-information on the programming model, register usage and calling conventions, and the application binary interface is provided. This information is particularly important when software development tools are generated from a processor model in order to realize function calls and enable interoperability with possibly existing third-party tools.

#### 1.1.2 Structural Languages

Structural processor description languages have their origins in hardware synthesis, similar to the hardware description languages VHDL and Verilog. These languages focus on a detailed model of the processor's hardware structure and organization. Structural processor models have several advantages that are attractive to processor designers. The languages usually provide abstractions like modules or components that have well-defined interfaces, and therefore, can be extended and exchanged easily. It is possible to develop libraries of components and combine them quickly to describe new processors or processor variants. This approach also resembles closely the traditional design using hardware description languages and thus lowers the initial effort to learn the concepts of a new specification language. In addition, structural models have a close coupling between the behavior of an instruction and the underlaying hardware components that implement that behavior. This is particularly useful for idiosyncratic architectures, where details of the hardware implementation are visible at the instruction set level.

On the downside, however, the instruction set of the processor is not specified explicitly. Instead, the instruction set needs to be extracted from the data path using static analysis techniques. The capabilities of this static analysis thus has a large impact on the usability of the specifications and may restrain the scope of the language. The hardware designers need to be well aware of the limitations and restrictions of the analysis to achieve the desired results.

Even if the analysis is able to extract the instruction set of the processor, it is often hard to determine the abstract behavior of the individual instructions. A particular implementation of a processor may realize the behavior specified by the instruction set architecture in different ways. Because of the detailed structural model these implementation peculiarities are visible to the tools processing the specification. For example, an implementation may choose to use dynamic branch prediction. The behavior of the branch predictor, its effect on the processor's state, and the interaction with all instructions that are possibly affected by the branch predication has to be analyzed in order to determine the exact semantics of branch instructions. Applications that require more abstract models of the instruction behavior are thus generally hard to realize using structural languages.

Most of these problems can be avoided by careful design of the language and by providing the right abstractions at the language level. Choosing the right level of abstraction is, however, still an open research problem. Part of this work is thus devoted to this issue.

#### 1.1.3 Mixed Languages

Over time languages that followed either the behavioral or the structural approach have started to gradually adopt ideas of languages following the other style. This lead to a new category of mixed processor description languages. Instead of focusing on one particular task most of these languages target a very broad spectrum of applications, ranging from high-level compiler generation to low-level hardware synthesis. Languages of this category combine the abstract view of the processor's instruction set with a detailed structural view of the hardware implementation. Consequently, the combined information allows the tools operating on the processor model to pick the view that is best suited for its particular task. Most contemporary languages follow this paradigm.

A major issue of mixed languages is the problem of redundancy. In order to be useful, both views need to capture a huge amount of information on the target processor, very often this information must be provided by the processor designer at different abstraction levels for the instruction set view and the structural view. If one view of the model is modified, the other view needs to be updated as well. Keeping the specifications consistent is thus a major challenge during the development and validation of a processor model. So far, tools that support automatic consistency checks are missing.

#### 1.1.4 Architecture Styles

Besides the specification paradigm, processor description languages can also be differentiated by the range of processor architectures that are supported. It is almost impossible to support all architectural styles and provide a generic platform that can be used to model *every* possible programmable system. In the domain of embedded systems relatively simple and efficient in-order pipelined processors are very common due to area and power constraints. Almost all processor description languages thus limit their primary focus on this class of processor architectures, either in the form of RISC or VLIW machines. The predominant architectural style in the general purpose computing domain, superscalar out-of-order architectures, is in turn not well supported.

## 1.2 Application of Processor Description Languages

As noted before, design space exploration is the main application scenario for processor description languages, i.e., the design of a new streamlined instruction processor for a particular application or application domain. The required tools to perform the exploration are (semi-)automatically derived from the processor model, including the compiler, assembler, linker and simulation tools. However, the information that is available in the processor models can be used in various ways independent from design space exploration. Figure 3 depicts the most common application fields targeted by many processor modeling frameworks.

Figure 3: Software development tools, test cases and even hardware models in a general purpose hardware description language can be derived from a processor model.

#### 1.2.1 Documentation and Design

The processor specifications capture a large amount of information on the internal organization of the processor and its instruction set in a formal and concise way. This model can easily be modified and extended and is well suited to communicate designs and design alternatives between development teams and engineers, the management, customers, and third-party vendors. In contrast to documentation in natural language these specifications are compact, more precise, and enable preliminary experiments in combination with the proper tools.

Some processor description languages even support the automatic generation of the processor manual and the instruction set reference manual. The formal architecture and instruction specifications are enriched with comments and documentation in natural language that are later compiled into a user manual.

#### 1.2.2 Verification and Validation

Related to the documentation and design of the processor is the verification and validation of the processor model, the processor implementation in hardware, and the accompanying software tools. During the product development cycle this phase is usually the most tedious and costly one. It is well known that problems encountered during an early phase of the product cycle are less costly to fix than in later phases. Processor description languages are a valuable tool to derive test suites and microbenchmarks early during the design. Even the structural equivalence between the processor model and hand-tuned HDL implementations of that processor can be verified using formal methods. In addition, software development can begin early

on, because of the availability of suitable development tools that are generated from the processor models. Consequently, problems can be spotted early and costs for validation and verification can be reduced later on.

#### 1.2.3 Assembler and Linker

The automatic generation of assembler, disassembler, and linker is supported by almost all processor description languages. Large portions of these tools are straightforward to generate once the assembly syntax and binary encoding of the individual instructions is known. However, supporting more advanced features such as relocation of symbols during linking, position independent code and dynamic linking, and debug information is considerable harder. The problem with these features usually arise from interoperability issues with existing system libraries, firmware, and operating systems. Capturing the conventions expected by these systems in the formal model of a processor description language is very hard and thus usually not well supported.

#### 1.2.4 Compiler

In comparison to other tasks, compiler generation is the most demanding application of processor description languages. A large number of compiler components are architecture-dependent and need to be customized for the target processor, most important are backend phases such as the register allocation, instruction scheduling, and instruction selection. But also optimizations that are applied in the middle-and frontend of a compiler are, to some degree, architecture-dependent. For example, the data representation and data layout in C/C++ frontends are architecture-dependent. Loop optimizations can be applied more efficiently when the optimization is aware of the supported addressing modes and the cache/memory organization, et cetera.

By far the most challenging task is the automatic generation of an optimizing instruction selector. During instruction selection the architecture independent intermediate representation of the compiler is translated to processor specific assembly or machine code. This translation has to preserve the semantics of the original program and should be efficient, i.e., the best possible instruction sequence should be selected that minimizes code size, execution time, and power consumption. The biggest obstacles are caused by limitations of the instruction set. The intermediate representation of the compiler is very general and is required to support all language features, in particular all arithmetic operations and addressing operations. Not all of these constructs can be implemented using a single instruction of the target processor. The behavior of constructs that can not be represented need to be emulated, or otherwise cause the compiler to fail during code generation. This emulation can be as simple as a sequence of instructions, but may also involve function calls to complex library routines, e.g., in the case of floating point operations. A second

problem that arises frequently are restrictions in the use of registers. If, during the computation of an expression a value is stored into a register, the instruction selector is required to ensure that all subsequent operations are able to retrieve this value. In particular in the case of application-specific instruction processors this kind of restrictions are very common.

#### 1.2.5 Instruction Set Simulator

A key component of all processor description and exploration systems is an accurate instruction set simulator that is capable to collect detailed statistics on the processor's behavior at runtime. In addition, simulation tools are valuable during software development for early prototyping as well as testing and debugging purposes. In both cases simulation speed is of utmost importance for the simulator to be actively used and accepted by the end users. Improving the simulation speed has thus been researched heavily in the past. Facing the rapid development of multi-core systems and complex systems-on-chip, efficient simulation tools can be expected to be a hot research topic for some time to come.

Simulators derived from processor models usually focus on the efficient simulation of a single processor core using interpretation as well as static and dynamic compilation techniques. These techniques are particularly useful for relatively deterministic in-order pipelined architectures, but fail to deliver the required performance in the presence of dynamic scheduling and speculative execution.

#### 1.2.6 Hardware Synthesis

Deriving hardware models is another challenging problem. The majority of systems is able to derive some form of VHDL or Verilog specification from a processor model that can then further be processed by synthesis tools or serve as a reference design for the handcrafted processor implementation.

Although VHDL and Verilog are in principle independent from the target technology many low-level constructs need to be expressed using vendor specific patterns and libraries to achieve optimal results. This applies to designs targeting *Field Programmable Gate Arrays* (FPGAs) and silicon processes alike. In particular in the case of behavioral languages the designer has very little control over the final hardware implementation. It is thus very hard to fine-tune the generated hardware model to improve chip area, clock frequency, and power consumption.

#### 1.2.7 Encoding Optimization

Defining and maintaining the specification of binary encoding of individual instructions is error prone and tedious, in particular during the early design phase when the

Figure 4: Structure of a compiler consisting of (a) a frontend, (b) an optimizing middleend, and (c) an architecture-dependent backend.

processor specification changes frequently. In many cases a very basic instruction encoding is sufficient for an initial performance evaluation using simulation. Some languages thus allow the encoding to be omitted and automatically derive a suitable instruction encoding. The designer may then choose to optimize this encoding manually or proceed with the tool-generated encoding. Some systems can even help to find an optimal encoding using execution profiles and static program statistics. These statistics are combined with the requirements of the individual instructions, i.e., the bits required to encode the instruction operands, and predefined constraints from the designer in order to minimize code size or reduce the complexity and power consumption of the instruction decoder in hardware.

## 1.3 Retargetable Compilation

A major application of processor description languages is the automatic or semiautomatic customization of a compiler. A compiler is a software program that translates a *source* program that is usually specified using a high-level language such as C or C++ to another *target* language [3, 140]. Typically the target language is *machine code* that can be processed efficiently by the processor of a computer system. Alternatively, the target language could be a *byte-code* representation of a virtual machine, such as the Java Virtual Machine, or, in the case of *source-to-source* translators, another high-level language. The translation usually involves some form of transformation or optimization intended to speed up the execution of the source

Figure 5: The three major phases of a compiler backend, instruction selection, instruction scheduling, and register allocation.

program on the target platform, reduce the static and/or dynamic memory requirements, or improve other metrics of interest. A compiler consists of three major components: (1) a frontend that reads and parses the source program and generates a generic representation of the program, (2) a largely target and source language independent middleend that transforms and optimizes the intermediate representation, and (3) a highly target-dependent backend that generates the final machine code. Most compilers follow this organization, possibly with slight variations, that is further detailed in Figure 4.

A special class of compilers are the so-called retargetable compilers. These systems are special in that the target-dependent components of the backend are very flexible and can quickly be adopted to a new instruction set or processor implementation. In the simplest form these target-dependent components are encapsulated in modules that are adopted manually to the new architecture. Some compilers come with specialized backend specification languages to simplify the retargeting. However, these specifications are typically tailored to the particular algorithms implemented within the compiler and, in particular, do not capture all implementation details of the processor. Instead, the backend specification is restricted to a very abstract model of the instruction set and the processor implementation that provides just enough information to guarantee an efficient and correct translation. If certain constraints of the processor can not be captured by the specification language, it is often necessary to manually extend or replace central components of the backend. Processor description languages show some similarities to these languages, but are typically more powerful and cover the processor design in more detail.

The backend is the central component of a retargetable compiler.<sup>1</sup> Most of the transformations and optimizations require knowledge about the target processor and thus need to be customized properly. Most modern compiler backends have a very similar organization, depicted in Figure 5. The *instruction selector* is one of the first

<sup>&</sup>lt;sup>1</sup>For some high-level languages the front- and middleend may also be architecture-dependent.

architecture-dependent translation steps. During this phase the intermediate representation of the compiler is transformed into a new representation that is very close to the actual machine instructions of the target processor. The main difference between this program representation and the final machine code are two-fold. For one, initially an infinite set of virtual registers represents local variables instead of actual registers that are available in the hardware. The register allocation phase later on calculates an assignment of the local variables to hardware registers and temporary memory locations and eliminates the virtual registers. Secondly, instructions with constant operands that are not yet fixed or memory operations that do not yet have a final addressing mode are represented by generic pseudo instructions. The pseudo instructions are replaced by concrete instructions once these values are known. The basic idea in both cases is to avoid premature assignment decisions. Another important backend phase is instruction scheduling. This phase is often applied twice once before register allocation, often referred to as prepass scheduling, and again after the assignment of local variables to hardware registers, usually referred to as postpass scheduling. The scheduling algorithm searches for an optimal ordering of the machine instructions in order to minimize the execution time of the program and optimally utilize the available hardware resources. In between the pre- and postpass scheduling phases the third backend phase is performed, the register allocation. Here, virtual registers are eliminated and replaced by hardware registers. If the number of hardware registers is not sufficient to hold all currently live values, spill code is generated. Occupied registers are disposed by storing the value currently held in the particular register to a temporary memory location. Corresponding memory load operations ensure that the proper value is available for later uses of the register. These additional store and restore operations may cause considerable overhead and thus need to be minimized.

The quality of the final machine code highly depends on the interaction between all three translation steps. This leads to *phase-ordering* issues, i.e., suboptimal results caused by an unfavorable interaction due to a bad ordering in which the phases are applied. For example, during instruction scheduling the resource utilization is maximized by exploiting the available parallelism in the program. Unfortunately, this adversely interacts with register allocation, because more data needs to be available in registers.

## 1.4 Scope and Contributions

This work presents a novel processor description language called \*ADL that is based on the generic markup language XML. \*ADL targets a wide range of application-specific instruction processors including RISC, CISC, and VLIW class architectures. General superscalar processor implementations with dynamic scheduling are not supported, however, in-order issue architectures with out-of-order execution and out-of-order completion can be modeled.

**x**ADL processor models primarily focus on the hardware organization, the language thus can be classified as a *structural* processor description language. In contrast to most traditional structural approaches, our language is intended to be applicable for all major application fields of classical processor description languages. In particular, good support for the automatic generation of software development tools such as the compiler, linker, and assembler was a primary design objective. But also the rather low-level tasks including simulator generation and hardware synthesis were considered as possible applications for our language. The main principles during the design of the language features were:

- Flexibility The \*ADL language was designed for a wide range of applications and architectures. This includes high-level and low-level tool generation, hardware modeling, as well as validation and verification tasks for a wide range of RISC, CISC, and VLIW processors.

- Compactness Short and readable specifications are easier to understand, maintain, and extend. It is thus important to provide powerful mechanisms to describe a possibly large number of instruction variants, the corresponding semantics and the hardware structure in a compact but still intuitive form. Redundant information should be avoided as much as possible.

- Reusability Processor designs are very often available in several variations that are largely compatible to each other but provide differing levels of performance, power, area, and cost trade-offs. \*ADL thus provides features to reuse and extend existing models, develop processor templates that can easily be adopted and modified, and build libraries of individual processor components.

- **Abstractions** Providing the right abstractions to the processor designer potentially simplifies the development and maintenance of processor models. In addition, these abstractions can radically simplify the tools that process the architecture models and thus improve the quality of all derived artifacts.

\*ADL specifications are comprised of four different sections: (1) the configuration section declares architecture parameters like the number of registers and functional units or the bit-width of the data path, (2) templates for assembly syntax, binary encoding, and ABI conventions are described in the meta-information section, (3) reusable blueprints of hardware components can be specified using types, (4) instances of the previously defined component types are finally interconnected to form the data path of the processor. The specification thus describes an abstract model of the processor's hardware organization. Individual instructions are not declared explicitly in our language, but instead are extracted from this structural model. The instruction set extraction follows very few simple rules and can efficiently be controlled by the processor designer. The resulting view of the instruction set is tightly coupled with the original structural model and provides both, an abstract notion of the instruction behavior and detailed information on how this behavior is

implemented in hardware. The combined information from both views allows a very flexible use of our language for low-level and high-level application scenarios.

In contrast to most contemporary processor description languages, we decided to follow the structural approach. Architecture designers often communicate their ideas using block diagrams and drawings of the hardware components and their interaction. Structural languages are conceptually very close to this approach and thus simplify the quick evaluation of ideas. However, structural languages also have drawbacks. Most notably these languages are not well suited for most high-level tasks such as compiler generation. The key principles during the design of the \*ADL language thus were the provision of proper abstractions and simplifications that ease the development of the processor models themselves and at the same time benefit the implementation of the software tools that process \*ADL models. The main contribution of this work can be summarized as follows:

- Component-based Modeling The processor description is composed from reusable components based on types. The user can build libraries from these types and can adopt and extend them for new designs using inheritance and generics, similar to classes and templates in C++.

- Flexible Templates Other parts of the specifications can also be reused across processor models. For example, templates that specify skeletons for the instruction encoding and syntax can be shared and reused. The instruction encoding specifications are very flexible and allow the modeling of various encoding styles, including variable-length and distributed variants.

- Abstractions Structural specifications usually describe the behavior of the individual hardware components in great detail. It is almost impossible to recognize common patterns for bypassing and forwarding as well as pipeline control. Our language provides abstractions to simplify the modeling of bypasses, pipelines, pipeline registers, and explicit communication between instructions for pipeline control.

- Instruction Set Extraction The instruction set of the processor is not specified explicitly, but is extracted from the structural specification using very simple rules. The instruction extraction can be controlled by the designer.

- Single Specification The instruction set extraction provides a behavioral view of the processor. Redundant specifications of the instruction behavior for simulation, synthesis, and compilation can thus be avoided. Only a single semantic specification of the instruction behavior is required.

- Backend Generation Highly optimizing backends for the open source compiler infrastructure LLVM and a proprietary compiler can be derived from **xADL** processor models. The derived compilers generate high-quality code that matches the performance of code generated by handcrafted compilers.

Speedups of up to 20% have been observed for individual benchmarks, on average a performance degradation of only 3%-15% has been measured.

- Compiler Completeness An important feedback for architecture designers is the completeness of the derived compiler, i.e., if the compiler is able to translate *all* valid programs accepted by the compiler frontend. A formal completeness test is presented that proves this property automatically. If our system is not able to guarantee completeness, counter examples are generated that guide architecture designer to improve the coverage or provide emulation routines for certain operations.

- Generator backends The feasibility of our approach has been demonstrated successfully by various other generator backends that allow high-quality simulation and development tools as well as hardware models to be derived from processor models.