Une école de l'IMT

Model-Driven Performance Evaluation and Formal Verification for Multi-level Embedded System Design

Daniela Genius, Letitia W. Li, Ludovic Apvrille

ludovic.apvrille@telecom-paristech.fr

Modelsward'2017

# Design Methodology of an Embedded System

System partitioning between HW and SW

- Functions  $\rightarrow$  execution nodes

- ► Communications between functions → communication and storage nodes

- Commonly "system-level partitioning" with (very) abstract models

# Design Methodology of an Embedded System

System partitioning between HW and SW

- Functions  $\rightarrow$  execution nodes

- ► Communications between functions → communication and storage nodes

- Commonly "system-level partitioning" with (very) abstract models

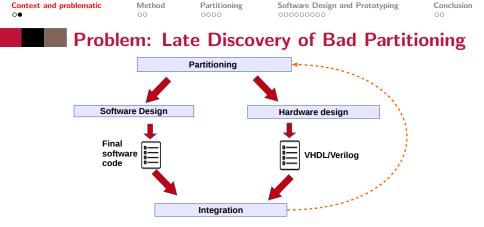

#### Software and hardware design

- Software and hardware and designed independently

- Integration phase

# Design Methodology of an Embedded System

System partitioning between HW and SW

- Functions  $\rightarrow$  execution nodes

- ► Communications between functions → communication and storage nodes

- Commonly "system-level partitioning" with (very) abstract models

#### Software and hardware design

- Software and hardware and designed independently

- Integration phase

Other contributions: Usually focused on one modeling aspect: difficult to iterate between partitioning and design

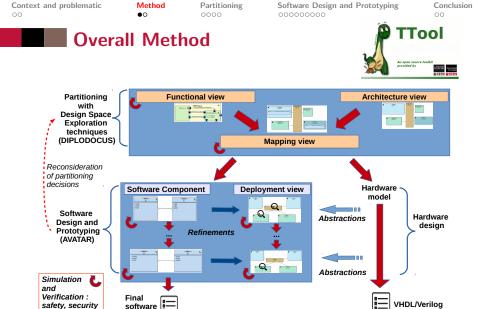

Our objective: A model-based approach with a close interaction between partitioning and software design

code

and

performance

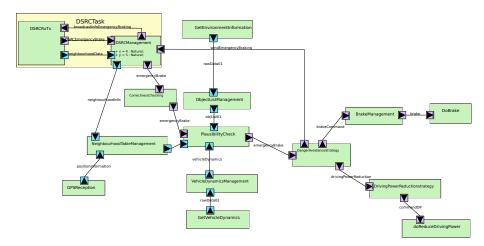

#### Case study: Automotive Braking Application

- Obstacle is detected by another automotive system that broadcasts this information to neighboring cars

- A car receiving such information has to decide if it is concerned with this obstacle

- Plausibility check function

- Decisions:

- Braking order

- Information forwarded to other neighboring cars

Method

Partitioning ●000 Software Design and Prototyping

Conclusion

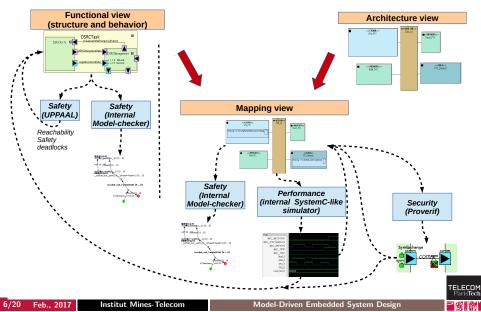

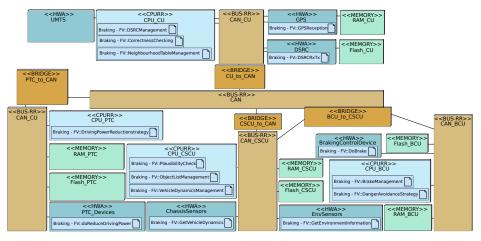

# **Partitioning Method**

### **Functional View**

Context and problematic

Method

Partitioning

Software Design and Prototyping

Conclusion

00

00

00

00

00

00

00

Method

Partitioning

Software Design and Prototyping

Conclusion

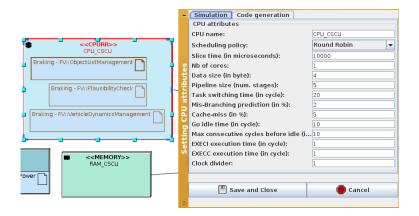

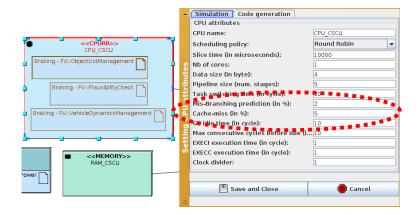

### Mapping View: CPU configuration

Method

Partitioning 000● Software Design and Prototyping

Conclusion

## Mapping View: CPU configuration

Method

Partitioning

Software Design and Prototyping

Conclusion

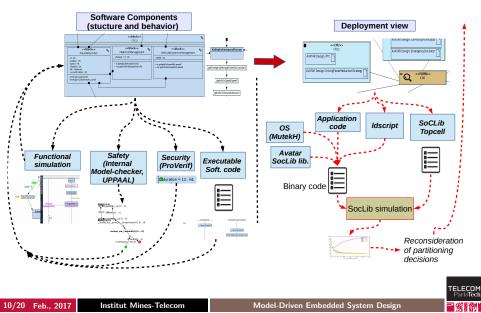

### Software Design Method

Method

Partitioning

Software Design and Prototyping

Conclusion

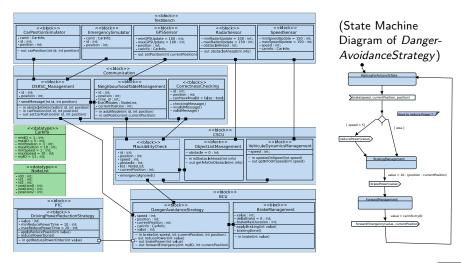

### **Software Components**

Method

Partitioning

Software Design and Prototyping

Conclusion

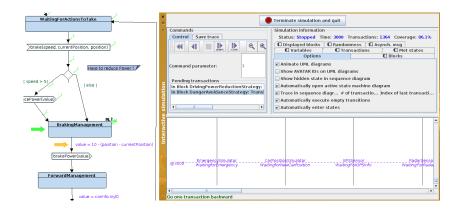

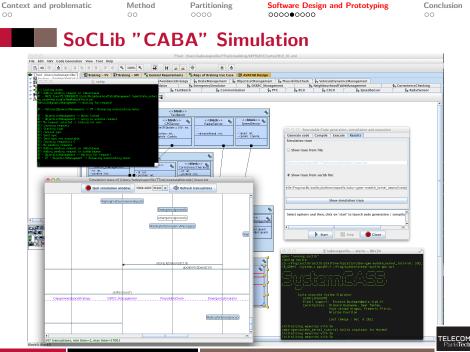

### Software Components: Simulation

Method

Partitioning

Software Design and Prototyping

Conclusion

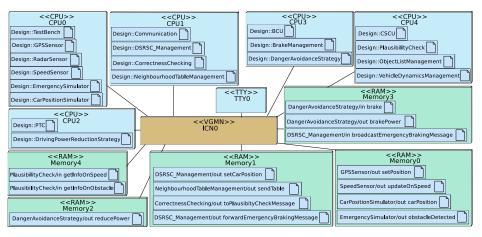

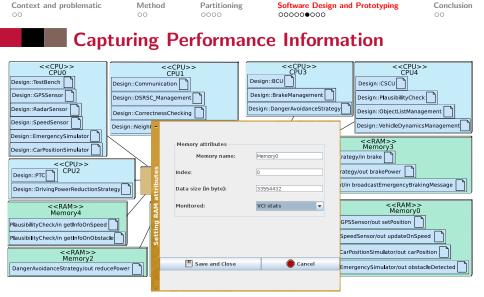

### **Deployment View**

14/20 Feb., 2017

Institut Mines-Telecom

Model-Driven Embedded System Design

- Logging probes can be set on CPU and memories

- Python-based scripts can generate curves from logs

Context and problematic

Method

Partitioning

Software Design and Prototyping

00

00

0000

000000000

Conclusion

### **Typical Performance Information**

- Overhead due to context switching (Cycles per Instruction)

- Memory access latency

- Data and instruction cache miss

- Bus contention

Context and problematic

Method

Partitioning

00

00

0000

0000

Software Design and Prototyping

Conclusion

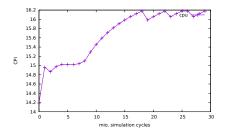

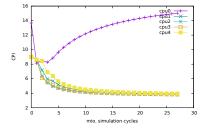

### **Performance Information: CPI**

#### Mono-processor configuration

#### 5-processor configuration

Context and problematic

Method

00

00

Software Design and Prototyping

Conclusion

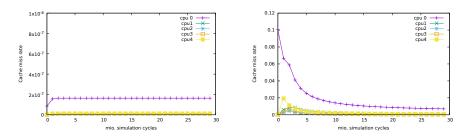

## **Performance Information: Cache Miss**

Partitioning

#### Data-cache miss

#### Instruction cache miss

(Configuration: 5 processors, 4 cache sets)

Method

Partitioning

Software Design and Prototyping

Conclusion •0

# Conclusion and Future Work

### Contributions

- Integration of system-level design space exploration and prototyping in the same toolkit

- Push-button approach to verification and simulation

- Deployment diagram: (in)validation of partitioning choices

#### What's next?

- Design Space Exploration, with automatically suggested modifications

- More detailed performance profiles (cache misses, buffer fill state etc.)

- Data cache miss per SysML block, latencies between states of the SMD, etc.

Method

Partitioning

Software Design and Prototyping

Conclusion ○●

#### **Thank You!**

#### References

- TTool: ttool.telecom-paristech.fr

- SoCLib: www.soclib.fr

Personal website: http://perso.telecom-paristech.fr/~apvrille