# A Coverage Driven Verification Environment for UML Models of Systems-on-Chip

Daniel Knorreck, Ludovic Apvrille, Renaud Pacalet {daniel.knorreck, ludovic.apvrille, renaud.pacalet}@telecom-paristech.fr System-on-Chip Laboratory (LabSoC), Institut Telecom, Telecom ParisTech, LTCI CNRS 2229 Route des Crêtes, B.P. 193, F-06904 Sophia Antipolis, France

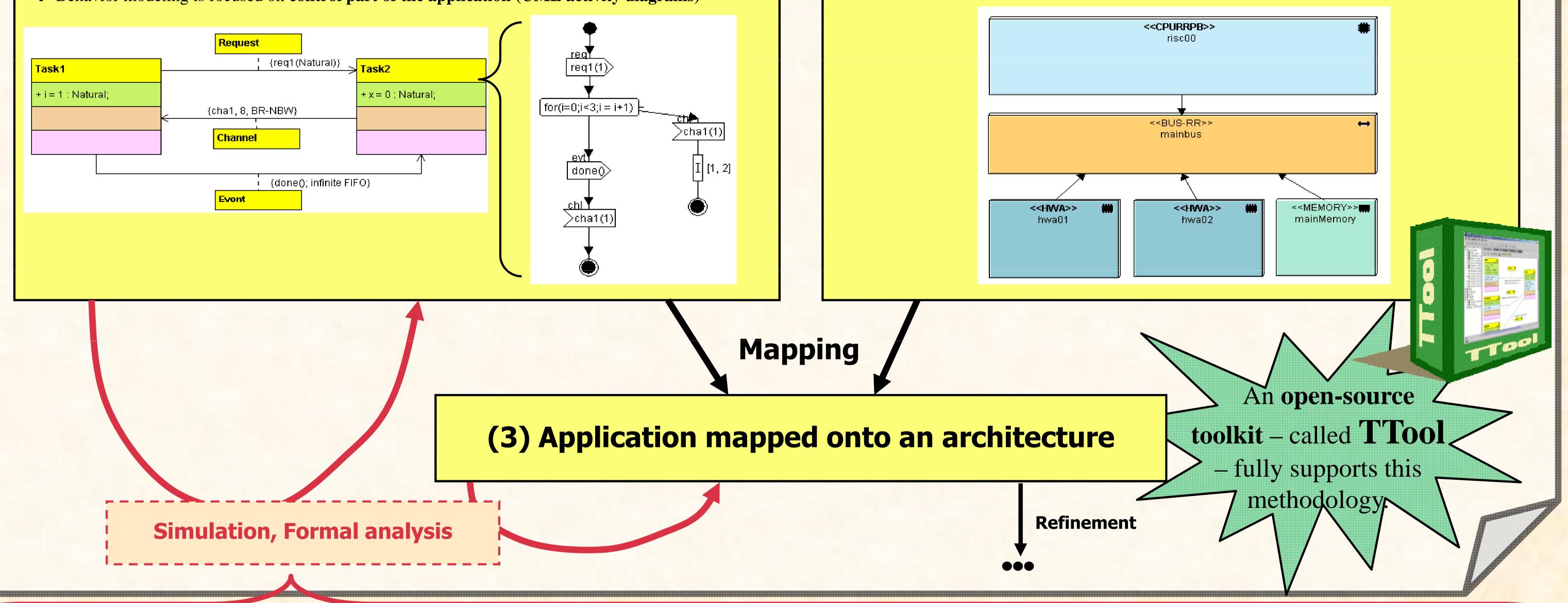

## **DIPLODOCUS: A 3-step Methodology Environment based on UML**

#### (1) Application Modelling

• System is modeled in terms of **communicating tasks** (**UML class diagram**)

• Behavior modeling is focused on **control part of the application (UML activity diagrams**)

#### (2) Architecture modelling

• Hardware architecture is modeled using **generic hardware components** (CPUs, buses, hardware accelerators)

- Computation and communication operations are abstracted using symbolic instructions

- Abstractions allow for fast simulation, transactions spanning hundreds of clock cycles are executed as a whole

- Possibility to generate traces in VCD format, as Gantt Diagrams and as reachability graphs

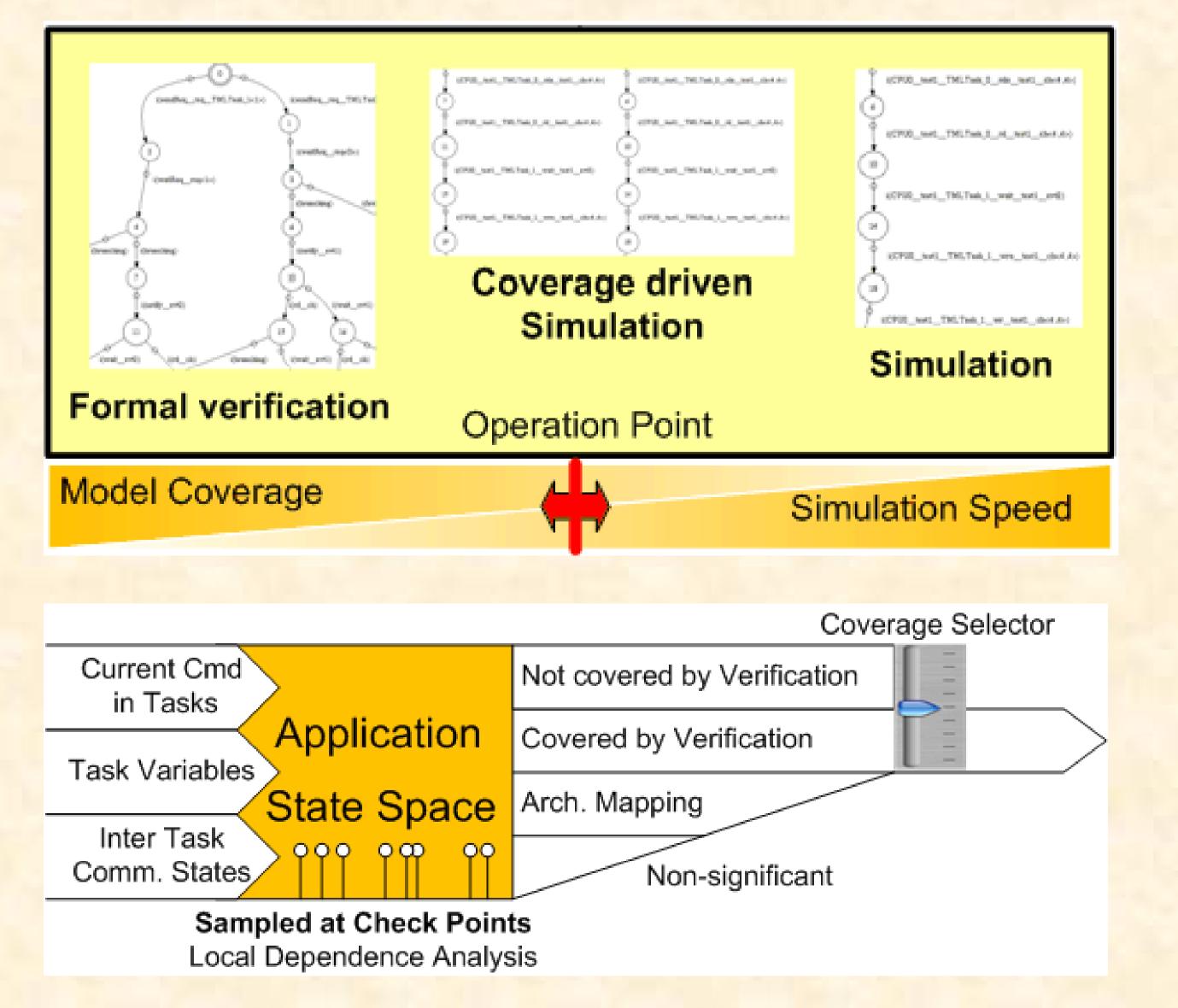

## **Variable Application Coverage**

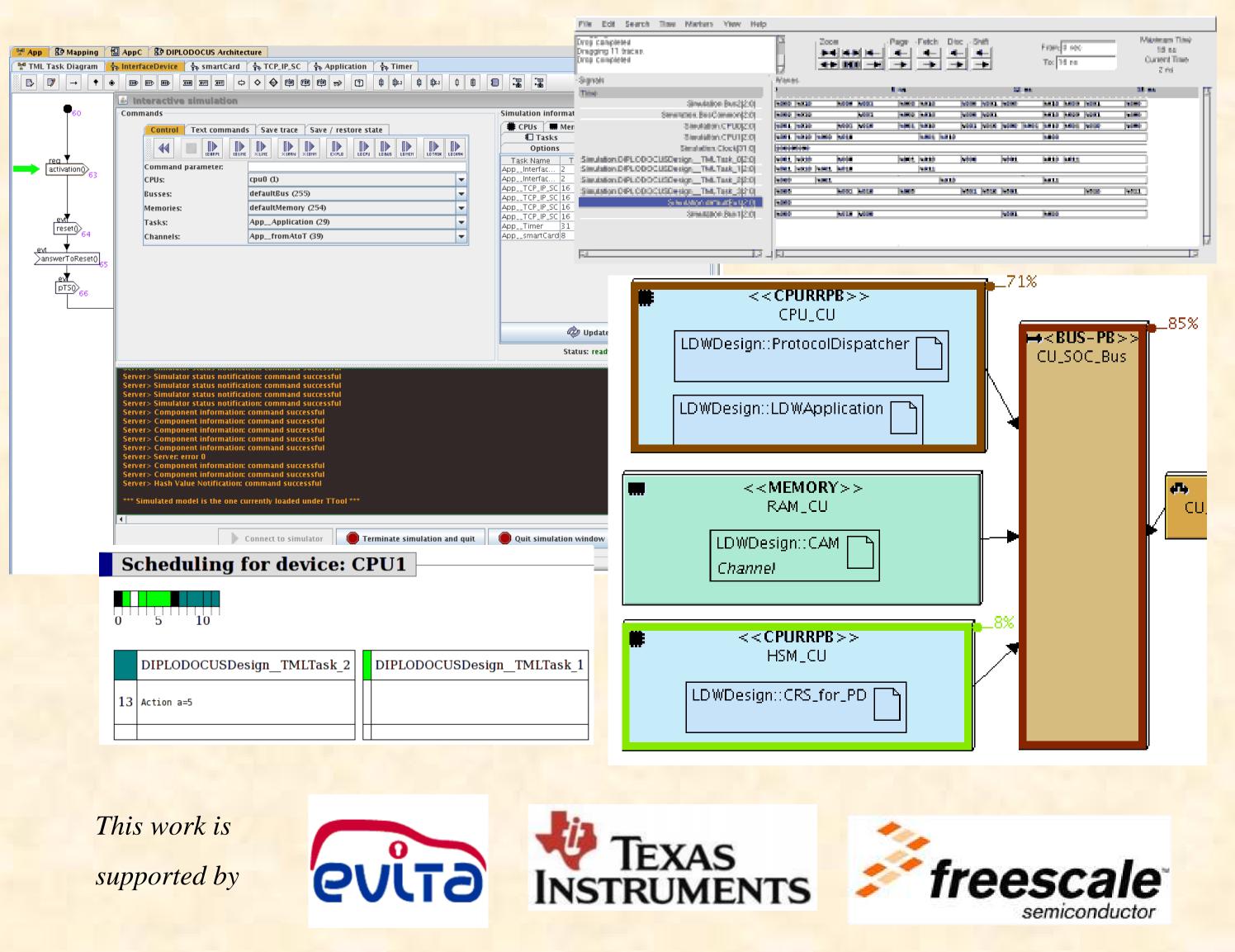

## **Interactive Simulation**

For a car communication application, we achieved an order of magnitude of simulation speed of **Billions of cycles/sec.**

A more fine grained model of an MPEG decoder led to a rate of Millions cycles/sec.

For further information: http://labsoc.comelec.enst.fr/ttool/