Product Version 5.0.13 December 2003  $\ensuremath{\mathbb{C}}$  1999-2003 Cadence Design Systems, Inc. All rights reserved. Printed in the United States of America.

Cadence Design Systems, Inc., 555 River Oaks Parkway, San Jose, CA 95134, USA

**Trademarks:** Trademarks and service marks of Cadence Design Systems, Inc. (Cadence) contained in this document are attributed to Cadence with the appropriate symbol. For queries regarding Cadence's trademarks, contact the corporate legal department at the address shown above or call 1-800-862-4522.

All other trademarks are the property of their respective holders.

**Restricted Print Permission:** This publication is protected by copyright and any unauthorized use of this publication may violate copyright, trademark, and other laws. Except as specified in this permission statement, this publication may not be copied, reproduced, modified, published, uploaded, posted, transmitted, or distributed in any way, without prior written permission from Cadence. This statement grants you permission to print one (1) hard copy of this publication subject to the following conditions:

- 1. The publication may be used solely for personal, informational, and noncommercial purposes;

- 2. The publication may not be modified in any way;

- 3. Any copy of the publication or portion thereof must include all original copyright, trademark, and other proprietary notices and this permission statement; and

- 4. Cadence reserves the right to revoke this authorization at any time, and any such use shall be discontinued immediately upon written notice from Cadence.

**Disclaimer:** Information in this publication is subject to change without notice and does not represent a commitment on the part of Cadence. The information contained herein is the proprietary and confidential information of Cadence or its licensors, and is supplied subject to, and may be used only by Cadence's customer in accordance with, a written agreement between Cadence and its customer. Except as may be explicitly set forth in such agreement, Cadence does not make, and expressly disclaims, any representations or warranties as to the completeness, accuracy or usefulness of the information contained in this document. Cadence does not warrant that use of such information will not infringe any third party rights, nor does Cadence assume any liability for damages or costs of any kind that may result from use of such information.

**Restricted Rights:** Use, duplication, or disclosure by the Government is subject to restrictions as set forth in FAR52.227-14 and DFAR252.227-7013 et seq. or its successor.

# Contents

| Preface                             | 23 |

|-------------------------------------|----|

| About This Manual                   | 23 |

| <u> 2 Dther Information Sources</u> | 23 |

| Documentation Conventions           | 25 |

| Text Command Syntax                 | 25 |

| <u>Using Menus</u>                  | 25 |

| <u>Using Forms</u>                  | 26 |

## 1 BuildGates Synthesis Command

| 3 | uildGates Synthesis Commands  | . 27 |

|---|-------------------------------|------|

|   | ac_shell                      | . 33 |

|   | add netconn                   | . 36 |

|   | alias                         | . 37 |

|   | all_children                  | . 38 |

|   | all parents                   | . 40 |

|   | bg shell                      | . 41 |

|   | bgx_shell                     | . 44 |

|   | check_netlist                 | . 47 |

|   | check option                  | . 49 |

|   | create instance               | . 52 |

|   | create_module                 | . 53 |

|   | create_net                    | . 54 |

|   | create_port                   | . 56 |

|   | delete attribute              | . 57 |

|   | delete aware component        | . 58 |

|   | delete_netconn                | . 59 |

|   | delete object                 | . 60 |

|   | delete unconnected ports      | . 61 |

|   | do blast busses               | . 62 |

|   | do build generic              | . 65 |

|   | do change module architecture |      |

| <u>do change name</u>                 |

|---------------------------------------|

| do cleanup netlist                    |

| <u>do copy module</u>                 |

| do create hierarchy                   |

| do delete buffer                      |

| do dissolve hierarchy                 |

| do extract critical                   |

| do extract fanin                      |

| do extract fanout                     |

| do extract non critical               |

| do fix hold                           |

| do insert buffer                      |

| <u>do_optimize</u>                    |

| <u>do pipeline check</u>              |

| do pipeline retime                    |

| <u>do pop module</u>                  |

| do push module                        |

| <u>do rebind</u>                      |

| do remove design                      |

| <u>do rename</u>                      |

| do uniquely instantiate               |

| do xform buffer                       |

| do xform buffer tree                  |

| do xform clone                        |

| do xform fast optimize                |

| do xform fix design rule violations   |

| do xform fix hold                     |

| do xform fix multiport nets           |

| do xform footprint                    |

| do xform ipo                          |

| do xform insert repeaters             |

| do xform map                          |

| do xform optimize generic             |

| do xform optimize slack               |

| do xform pre placement optimize slack |

| do xform prevent crosstalk 146        |

| do xform prevent wire self heat 148 |

|-------------------------------------|

| do xform propagate constants 149    |

| do xform reclaim area               |

| do xform remove redundancy 152      |

| do xform resize                     |

| do xform restructure                |

| do xform run repair file            |

| do xform structure                  |

| do xform unmap                      |

| <u>dump_adb</u>                     |

| eval bottom up                      |

| <u>find</u>                         |

| <u>get area</u>                     |

| get attribute                       |

| get build id                        |

| get buswidth                        |

| get cell area                       |

| get crosstalk threshold             |

| get crosstalk tolerance             |

| get current instance                |

| get current module                  |

| get equivalent cells                |

| get global                          |

| get hdl file                        |

| get hdl hierarchy                   |

| get hdl top level                   |

| get hdl type                        |

| <u>get info</u>                     |

| get message count                   |

| get message verbosity               |

| <u>get names</u>                    |

| <u>get net</u>                      |

| get parent instances                |

| get state of design                 |

| get tempfilename                    |

| get version                         |

| <u>help</u>                      |

|----------------------------------|

| <u>highlight</u>                 |

| issue message                    |

| <u>limit</u>                     |

| <u>quit</u>                      |

| <u>read adb</u>                  |

| <u>read_edif</u>                 |

| <u>read symbol</u>               |

| read symbol update               |

| read_verilog216                  |

| <u>read_vhdl</u>                 |

| <u>record macro</u>              |

| report area                      |

| report aware library             |

| report crosstalk violations      |

| report design rule violations    |

| <u>report_fsm</u>                |

| report globals                   |

| report hierarchy                 |

| report path group options        |

| report resources                 |

| report_skewed_clock_pins245      |

| report vhdl library              |

| report wire self heat violation  |

| reset crosstalk threshold        |

| reset_dont_modify                |

| reset failsafe                   |

| <u>reset_global</u>              |

| reset register type              |

| reset vhdl library               |

| reset_wire_self_heat_prevention  |

| set_attribute                    |

| set aware component property 261 |

| set_aware_library                |

| set cell property                |

| set current instance             |

| set current module     |

|------------------------|

| set dissolve hierarchy |

| set dont modify        |

| <u>set_failsafe</u>    |

| <u>set global</u>      |

| <u>set logic0</u> 273  |

| <u>set_logic1</u>      |

| set message count      |

| set message verbosity  |

| set_path_group_options |

| set port property      |

| set register type      |

| set table style        |

| set unconnected        |

| set vhdl library       |

| <u>unalias</u>         |

| <u>write adb</u>       |

| <u>write edif</u>      |

| write globals          |

| write verilog          |

| <u>write vhdl</u>      |

## 2 CTPKS Commands.

| CIPKS Commands               | 298 |

|------------------------------|-----|

| do build clock tree          | 300 |

| do build physical tree       | 305 |

| do xform optimize clock tree | 308 |

| get clock tree constraints   | 317 |

| get clock tree objects       | 318 |

| report clock tree            | 320 |

| report_clock_tree_violations | 327 |

| reset clock tree constraints | 329 |

| set clock tree constraints   | 330 |

| <u>define_structure</u>      | 333 |

| <u>Attributes</u>            | 336 |

## 3 Distributed Synthesis Commands

| ) | stributed Synthesis Commands | 340 |

|---|------------------------------|-----|

|   | check batch                  | 342 |

|   | check dist                   | 344 |

|   | check host                   | 345 |

|   | get host info                | 346 |

|   | get job info                 | 349 |

|   | get_weight_batch_option      | 355 |

|   | <u>kill job</u>              | 356 |

|   | remove host                  |     |

|   | remove_job                   | 359 |

|   | report job                   |     |

|   | reset dist bits              | 361 |

|   | reset dist rlimit            |     |

|   | reset dist point             |     |

|   | reset dist weight            |     |

|   | set dist bits                |     |

|   | set dist point               |     |

|   | set dist rlimit              |     |

|   | set host config              |     |

|   | set host list                |     |

|   | set dist weight              |     |

|   | set_weight_batch_option      | 374 |

## <u>4</u>

| Low Power Synthesis (LPS) Commands |

|------------------------------------|

| <u>check_cg_logic</u> 37           |

| do remove cg dummy hierarchy       |

| do_xform_insert_sleep_mode38       |

| do xform optimize clock gate       |

| do xform optimize power            |

| get_clock_gating_options           |

| get clock tree power               |

| <u>get dynamic peak power</u>      |

| get dynamic power                                    |

|------------------------------------------------------|

| get gating instance list                             |

| get list of cg instances                             |

| get power                                            |

| get power display unit 402                           |

| get power optimization options 403                   |

| get sleep mode instance list 404                     |

| get sleep mode options                               |

| <u>read saif</u>                                     |

| <u>read_tcf</u>                                      |

| read tcf update                                      |

| <u>read vcd</u>                                      |

| report clock gating                                  |

| report power                                         |

| report slew for power analysis 431                   |

| report to stats                                      |

| reset slew for power analysis 437                    |

| reset switching activity                             |

| set clock gating options                             |

| set power display unit                               |

| set power optimization options                       |

| set sleep mode options                               |

| set slew for power analysis 459                      |

| set switching activity                               |

| write clock gating attribute 463                     |

| <u>write_psf</u>                                     |

| write sleep mode attribute 466                       |

| <u>write_tcf</u>                                     |

| Low Power for Existing BuildGates Synthesis Commands |

# <u>5</u>

| PKS Commands                             | 474 |

|------------------------------------------|-----|

| add physical connection                  | 479 |

| <u>check_design</u>                      | 481 |

| check libraries and design compatibility | 482 |

| check_library                     |

|-----------------------------------|

| create blockage                   |

| create layer usages table 488     |

| create physical cluster           |

| create physical instance          |

| create physical net               |

| create physical pin               |

| create placement area             |

| do extract lef model              |

| do extract route parasitics       |

| <u>do groute</u>                  |

| do initialize floorplan           |

| do insert filler cells            |

| <u>do place</u>                   |

| <u>do pull</u>                    |

| <u>do_push</u>                    |

| do refine place                   |

| do remove filler cells            |

| do remove route                   |

| do reset floorplan                |

| <u>do route</u>                   |

| <u>do_wroute</u>                  |

| <u>do wroute eco</u>              |

| do xform tcorr eco                |

| generate supply rails on rows 554 |

| <u>get cluster</u>                |

| get cluster contents              |

| get cluster names                 |

| get cluster physical info         |

| get current cluster               |

| get current congestion            |

| get current utilization           |

| get ground net                    |

| get library layer_offset          |

| get logic 0 net                   |

| get logic 1 net                   |

| get min porosity for over block routing |

|-----------------------------------------|

| get min wire length                     |

| get physical info                       |

| get pin location                        |

| get power net                           |

| get route availability                  |

| get special netpins                     |

| get steiner capacitance                 |

| get steiner channel width 577           |

| get steiner length                      |

| get steiner resistance                  |

| modify physical cluster                 |

| <u>pks_shell</u>                        |

| <u>prune_routes</u>                     |

| read cap table                          |

| read cap table update                   |

| read_change_file                        |

| <u>read_def</u>                         |

| <u>read_gns</u>                         |

| read layer usages                       |

| <u>read lef</u>                         |

| read lef update                         |

| <u>read_pdef</u>                        |

| <u>read wdb</u>                         |

| remove blockage                         |

| remove physical cluster                 |

| remove physical connection              |

| remove_physical_instance                |

| remove physical net                     |

| remove physical pin                     |

| remove_placement_area                   |

| remove supply rails on rows 610         |

| report block halo                       |

| report blockage                         |

| report cluster                          |

| report floorplan parameters             |

| report grow parameters                      |

|---------------------------------------------|

| report net distribution                     |

| report net rc                               |

| report_overlap                              |

| report physical library                     |

| report placement area                       |

| report preroute parameters                  |

| report supply rails on rows                 |

| report unplaced                             |

| reset dont move                             |

| reset net physical attribute                |

| set block halo                              |

| set block rc rule                           |

| set current cluster                         |

| set default core site                       |

| set dont move                               |

| set floorplan parameters                    |

| set ground net                              |

| set grow anchors                            |

| set grow parameters                         |

| set layer usages table 644                  |

| set lef_multiplier                          |

| set library layer offset 648                |

| set logic 0 net                             |

| <u>set logic 1_net</u>                      |

| set min porosity for over block routing 651 |

| set min RC multipliers                      |

| set min wire length 654                     |

| set net physical attribute                  |

| set physical info                           |

| set physical instance                       |

| set pin location                            |

| set pin status                              |

| set power_net                               |

| set power stripe spec                       |

| set preroute parameters                     |

| set route availability        |

|-------------------------------|

| set special netpin            |

| set steiner channel width 673 |

| set_steiner_mode              |

| set supply rails on rows      |

| vbg pks display ilist         |

| vbg_pks_group_delete          |

| vbg pks group display         |

| <u>write def</u>              |

| <u>write_gns</u>              |

| write gns lib                 |

| write layer usages            |

| <u>write_pdef</u>             |

| write wdb                     |

## <u>6</u> Te

| <u>e</u> | est Synthesis Commands             | 690 |

|----------|------------------------------------|-----|

|          | check dft rules                    | 692 |

|          | display_scan_chains                | 695 |

|          | do remove scan order data          | 697 |

|          | do xform connect scan              | 698 |

|          | do xform fix dft_violations        | 704 |

|          | do xform insert shadow dft         | 706 |

|          | do xform insert testpoint          | 712 |

|          | get_dft_config_mode                | 716 |

|          | get scan chain info                |     |

|          | read scan order file               | 720 |

|          | remove dft assertions              | 722 |

|          | report dft assertions              | 726 |

|          | report dft registers               |     |

|          | reset dft compatible clock domains | 731 |

|          | reset dft fix violations           | 732 |

|          | reset dft internal clock domain    |     |

|          | reset_dft_transparent              | 734 |

|          | reset dont scan                    | 736 |

| reset dont touch scan            |

|----------------------------------|

| reset must scan                  |

| reset scan data                  |

| reset_test_mode_setup            |

| set dft clock waveform           |

| set dft compatible clock domains |

| set dft compatible chains        |

| set dft fix violations           |

| set dft internal clock domain    |

| set dft lockup element           |

| set dft transparent              |

| set dont scan                    |

| set dont touch scan              |

| set lssd aux clock               |

| set Issd scan clock a            |

| set Issd scan clock b            |

| set max scan chain length        |

| set must scan                    |

| set number of scan chains        |

| set scan chain                   |

| set scan chain segment           |

| set scan data                    |

| set scan equivalent              |

| set scan mode                    |

| set scan style                   |

| set test mode setup              |

| set test scan clock              |

| write atpg info                  |

| write scan order file            |

# 7

| Common Timing Engine (CTE) Commands | 788 |

|-------------------------------------|-----|

| Path Exception Priorities           | 797 |

| Bidirectional Pin Defaults          | 799 |

| Command Descriptions                | 802 |

| <u>check_timing</u>               |

|-----------------------------------|

| create mp constraint arc          |

| create mp delay arc               |

| create mp drive type              |

| create mp load type               |

| create mp model                   |

| create mp path type               |

| create mp port                    |

| do analyze crosstalk              |

| do cppr analysis                  |

| do derive context                 |

| do extract model                  |

| do signalstorm                    |

| do time budget                    |

| do xform timing correction        |

| get capacitance unit              |

| get cell drive                    |

| get cell pin load                 |

| <u>get_clock</u>                  |

| get clock propagation             |

| get clock source                  |

| get constant for timing           |

| get dcl calculation mode          |

| get dcl functional mode           |

| get dcl functional mode array 863 |

| get dcl level                     |

| get derived clock                 |

| <u>get drive pin</u>              |

| get fanin                         |

| <u>get fanout</u>                 |

| get flow compatible mode          |

| get load pin                      |

| get module worst slack            |

| get operating conditions          |

| get operating parameter           |

| get operating voltage             |

| get propagated clock        |

|-----------------------------|

| get scale delays            |

| <u>get slack</u>            |

| get slew thresholds         |

| get tech info               |

| get time borrow limit       |

| <u>get time unit</u>        |

| get timing                  |

| get top timing module       |

| <u>libcompile</u>           |

| load dcl rule               |

| <u>read alf</u>             |

| <u>read_ctlf</u>            |

| read dc script              |

| read dotlib                 |

| <u>read irdrop</u>          |

| read library update         |

| <u>read_ola</u>             |

| read sdf                    |

| <u>read_spef</u>            |

| <u>read_spf</u>             |

| <u>read_stamp</u>           |

| <u>read_tlf</u>             |

| remove assertions           |

| report analysis coverage    |

| report annotated check      |

| report_annotations          |

| report cell instance        |

| report cell instance timing |

| report clocks               |

| report fanin                |

| report fanout               |

| report functional mode      |

| report inactive arcs        |

| report library              |

| <u>report_net</u>                | . 975 |

|----------------------------------|-------|

| report path exceptions           |       |

| report path groups               |       |

| report path group timing         |       |

| report poles residues            |       |

| report ports                     |       |

| report_timing                    |       |

| reset capacitance limit          |       |

| reset capacitance unit           |       |

| reset clock gating check         |       |

| reset clock info change          |       |

| reset clock insertion delay      | 1020  |

| reset_clock_root                 |       |

| reset clock uncertainty          |       |

| reset constant for timing        |       |

| reset_dcl_calculation_mode       |       |

| reset dcl functional mode        |       |

| reset dcl level                  |       |

| reset_default_slew_time          | 1031  |

| reset disable cell timing        |       |

| reset disable clock gating check |       |

| reset disable timing             | 1035  |

| reset drive cell                 |       |

| reset drive resistance           |       |

| reset_external_delay             |       |

| reset fanout load                | 1043  |

| reset fanout load limit          |       |

| reset feedback loop snipped arcs | 1045  |

| reset functional mode            |       |

| reset generated clock            | 1047  |

| reset_ideal_net                  |       |

| reset input delay                |       |

| reset num external sinks         |       |

| reset_num_external_sources       |       |

| reset operating condition        | 1053  |

| reset operating parameter        | 1055  |

| reset operating voltage 1056    |

|---------------------------------|

| reset path exception            |

| reset path group                |

| reset port capacitance          |

| reset port capacitance limit    |

| reset port wire load            |

| reset propagated clock          |

| reset scale delays              |

| reset slew limit                |

| reset slew thresholds           |

| reset slew time                 |

| reset slew time limit           |

| reset tech info                 |

| reset time borrow limit         |

| reset time unit                 |

| reset wire capacitance          |

| reset wire load                 |

| reset wire load mode            |

| reset wire load selection table |

| reset wire resistance           |

| save mp model                   |

| set annotated check 1094        |

| set annotated delay 1096        |

| set capacitance limit           |

| set capacitance unit            |

| set case analysis 1104          |

| set cell pin load 1106          |

| <u>set_clock</u>                |

| set clock arrival time          |

| set clock gating check 1112     |

| set_clock_info_change           |

| set clock insertion delay 1120  |

| set clock propagation           |

| set clock_required_time         |

| <u>set clock root</u>           |

| set clock transition            |

| set_clock_uncertainty          | 1130 |

|--------------------------------|------|

| set constant for timing        | 1134 |

| set cycle addition             |      |

| set_data_arrival_time          | 1143 |

| set data required time         |      |

| set dcl calculation mode       |      |

| set dcl_functional_mode_       | 1146 |

| set dcl level                  |      |

| set default slew time          |      |

| set disable cell timing        | 1149 |

| set disable clock gating check |      |

| set disable timing             |      |

| set drive_cell                 | 1156 |

| set drive resistance           |      |

| set external delay             |      |

| set false path                 |      |

| set fanout load limit          |      |

| set flow compatible mode       |      |

| set functional mode            |      |

| set generated clock            | 1184 |

| set ideal net                  |      |

| set input delay                | 1193 |

| set max_delay                  |      |

| set min delay                  |      |

| set mp area                    |      |

| set mp global parameter        | 1199 |

| set mp max fanout limit        |      |

| set mp min fanout limit        | 1202 |

| set mp port drive              |      |

| set mp port load               | 1205 |

| set mp_port_max_capacitance    | 1207 |

| set mp port max transition     | 1209 |

| set mp port min capacitance    | 1211 |

| set mp port min transition     | 1213 |

| set mp_technology              | 1215 |

| set num external sinks         | 1217 |

| set num_external_sources         |     |

|----------------------------------|-----|

| set operating conditions         | 219 |

| set operating parameter          |     |

| set operating voltage            | 228 |

| set path_delay_constraint12      | 230 |

| set path group                   |     |

| set port capacitance             | 238 |

| set port capacitance limit       |     |

| set port wire load               |     |

| set propagated clock             | 244 |

| set scale delays                 | 246 |

| set slew limit                   | 248 |

| set slew thresholds              | 249 |

| set slew time                    |     |

| set slew time limit              | 253 |

| set tech info                    |     |

| set time borrow limit            | 263 |

| set time unit                    |     |

| set top timing module            | 267 |

| set wire capacitance             | 269 |

| set wire load                    | 271 |

| set wire load mode               | 274 |

| set wire load selection table 12 |     |

| set wire resistance              | 276 |

| unload dcl rule                  | 277 |

| write assertions                 | 278 |

| write constraints                | 280 |

| write gcf assertions             | 282 |

| write library assertions         | 284 |

| <u>write rspf</u>                | 285 |

| <u>write_sdc</u>                 | 286 |

| <u>write sdf</u>                 | 288 |

| <u>write spf</u>                 | 295 |

| write timing windows             | 296 |

# <u>1</u>

| Temporary Commands 129                         | 8  |

|------------------------------------------------|----|

| Timing Analysis on page 1310Datapath Synthesis | 9  |

| <u>write datapath pdef</u> 130                 | 0  |

| Turning on the Prototype DP GUI 130            | )1 |

| <u>Optimization</u>                            | 12 |

| <u>get cell area</u>                           | 13 |

| <u>get_cell_pin_load</u> 130                   | )4 |

| <u>set cell area</u>                           | )5 |

| <u>set cell pin load</u>                       | 6  |

| <u>PKS</u> 130                                 | )7 |

| <u>generate lut from routes</u> 130            | 8  |

| report steiner route                           | 19 |

| Timing Analysis                                | 0  |

| <u>convert delays to assertions</u> 131        | 1  |

| <u>get cell area</u>                           | 2  |

| <u>set_cell_area</u>                           | 3  |

| write design timing                            | 4  |

| write timing windows clock arrival             | 6  |

| <u>write_timing_windows_fast_mode</u> 131      | 7  |

| write timing windows slack info                | 8  |

|                                                |    |

| Index                                          | 20 |

# Preface

This preface contains the following sections:

- About This Manual on page 23

- <u>Other Information Sources</u> on page 23

- <u>Documentation Conventions</u> on page 25

## **About This Manual**

This manual is a complete alphabetical collection of BuildGates synthesis commands. BuildGates synthesis can be run both in command line mode and in graphical user interface (GUI) mode.

## **Other Information Sources**

For more information about related products, you can consult the sources listed here. The documents you have vary depending on your product licenses.

- AmbitWare Component Reference

- BuildGates Synthesis User Guide

- CeltIC User Guide

- Common Timing Engine (CTE) User Guide

- Constraint Translation for BuildGates Synthesis and Cadence PKS

- Datapath for BuildGates Synthesis and Cadence PKS

- Delay Calculation Algorithm Guide

- Design for Test Using BuildGates Synthesis and Cadence PKS

- Distributed Processing for BuildGates Synthesis

- Glossary for BuildGates Synthesis and Cadence PKS

- GUI Guide for BuildGates Synthesis and Cadence PKS

- HDL Modeling for BuildGates Synthesis

- Low Power for BuildGates Synthesis and Cadence PKS

- Low Power Synthesis Tutorial

- Migration Guide for BuildGates Synthesis and Cadence PKS

- Modeling Generation for Verilog 2001 and the Verilog Datapath Extension

- PKS User Guide

- Synthesis Place-and-Route Flow Guide

- Verilog Datapath Extension Reference

- VHDL Datapath Package Reference

- Known Problems and Solutions in BuildGates Synthesis

- Know Problems and Solutions in Cadence PKS

- What's New in Cadence PKS

- What's New in BuildGates Synthesis

BuildGates synthesis is often used with other Cadence<sup>®</sup> tools during various design flows. The following documents provide information about these tools and flows. Availability of these documents depends on the product licenses your site has purchased.

- Cadence Timing Library Format Reference

- Cadence Pearl Timing Analyzer User Guide

- Cadence General Constraint Format Reference

The following books are helpful references, but are not included with the CD-ROM documentation:

- IEEE 1364 Verilog HDL LRM

- TCL Reference, Tcl and the Tk Toolkit, John K. Ousterhout, Addison-Wesley Publishing Company

## **Documentation Conventions**

#### **Text Command Syntax**

The list below describes the syntax conventions used for the BuildGates Synthesis text interface commands.

| literal  | Nonitalic words indicate keywords that you must enter literally.<br>These keywords represent command or option names.                                                                                                                                                                           |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| argument | Words in italics indicate user-defined arguments or information for which you must substitute a name or a value.                                                                                                                                                                                |

| I        | Vertical bars (OR-bars) separate possible choices for a single argument.                                                                                                                                                                                                                        |

| [ ]      | Brackets denote optional arguments. When used with OR-bars, they enclose a list of choices from which you can choose one.                                                                                                                                                                       |

| { }      | Braces are used to indicate that a choice is required from the list<br>of arguments separated by OR-bars. You must choose one from<br>the list.                                                                                                                                                 |

|          | { argument1   argument2   argument3 }                                                                                                                                                                                                                                                           |

|          | Three dots () indicate that you can repeat the previous argument. If the three dots are used with brackets (that is, [argument]), you can specify zero or more arguments. If the three dots are used without brackets (argument), you must specify at least one argument, but can specify more. |

| #        | The pound sign precedes comments in command files.                                                                                                                                                                                                                                              |

#### **Using Menus**

GUI commands can take one of three forms.

| CommandName | A command name with no dots or arrow executes immediately.           |

|-------------|----------------------------------------------------------------------|

| CommandName | A command name with three dots displays a form for choosing options. |

| CommandName -> | A command name with a right arrow displays an additional menu with more commands. Multiple layers of menus and commands are presented in what are called command sequences, for example: $File - Import - LEF$ . In this example, you go to the File menu, then the Import submenu, and, finally, the LEF command. |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Using Forms    |                                                                                                                                                                                                                                                                                                                    |

|                | A menu button that contains only three dots provides browsing capability. When you select the browse button, a list of choices appears.                                                                                                                                                                            |

| Ok             | The Ok button executes the command and closes the form.                                                                                                                                                                                                                                                            |

| Cancel         | The Cancel button cancels the command and closes the form.                                                                                                                                                                                                                                                         |

| Defaults       | The <i>Defaults</i> button displays default values for options on the form.                                                                                                                                                                                                                                        |

| Apply          | The <i>Apply</i> button executes the command but does not close the form.                                                                                                                                                                                                                                          |

# 1

# **BuildGates Synthesis Commands**

This chapter describes the commands and global variables used with BuildGates<sup>®</sup> Synthesis.

- <u>ac\_shell</u> on page 33

- <u>add\_netconn</u> on page 36

- alias on page 37

- <u>all children</u> on page 38

- <u>all parents</u> on page 40

- bg shell on page 41

- bgx shell on page 44

- <u>check netlist</u> on page 47

- <u>check\_option</u> on page 49

- <u>create instance</u> on page 52

- <u>create module</u> on page 53

- <u>create\_net</u> on page 54

- <u>create port</u> on page 56

- <u>delete attribute</u> on page 57

- <u>delete\_aware\_component</u> on page 58

- <u>delete\_netconn</u> on page 59

- <u>delete object</u> on page 60

- <u>delete\_unconnected\_ports</u> on page 61

- <u>do blast busses</u> on page 62

- <u>do build generic</u> on page 65

- <u>do change module architecture</u> on page 70

- <u>do change name</u> on page 72

- <u>do cleanup netlist</u> on page 77

- <u>do\_copy\_module</u> on page 78

- <u>do create hierarchy</u> on page 80

- <u>do delete buffer</u> on page 82

- <u>do\_dissolve\_hierarchy</u> on page 83

- <u>do extract critical</u> on page 85

- <u>do extract fanin</u> on page 88

- <u>do\_extract\_fanout</u> on page 90

- <u>do extract non critical</u> on page 92

- <u>do fix hold</u> on page 93

- <u>do insert buffer</u> on page 95

- <u>do optimize</u> on page 97

- <u>do pipeline check</u> on page 112

- <u>do pipeline retime</u> on page 113

- <u>do pop module</u> on page 114

- <u>do push module</u> on page 115

- <u>do\_rebind</u> on page 116

- <u>do remove design</u> on page 119

- <u>do rename</u> on page 120

- <u>do\_uniquely\_instantiate</u> on page 122

- <u>do xform buffer</u> on page 124

- <u>do xform buffer tree</u> on page 126

- <u>do\_xform\_clone</u> on page 128

- <u>do xform fast optimize</u> on page 130

- <u>do xform fix design rule violations</u> on page 132

- <u>do\_xform\_fix\_hold</u> on page 134

- <u>do xform fix multiport nets</u> on page 136

- <u>do xform footprint</u> on page 137

- <u>do\_xform\_ipo</u> on page 138

- <u>do xform insert repeaters</u> on page 139

- <u>do xform map</u> on page 141

- <u>do\_xform\_optimize\_generic</u> on page 143

- <u>do xform optimize slack</u> on page 144

- <u>do xform pre placement optimize slack</u> on page 145

- <u>do\_xform\_prevent\_crosstalk</u> on page 146

- <u>do xform prevent wire self heat</u> on page 148

- <u>do xform propagate constants</u> on page 149

- <u>do xform reclaim area</u> on page 150

- <u>do xform remove redundancy</u> on page 152

- <u>do xform resize</u> on page 153

- <u>do\_xform\_restructure</u> on page 155

- <u>do xform run repair file</u> on page 156

- <u>do xform structure</u> on page 161

- <u>do\_xform\_unmap</u> on page 163

- <u>dump\_adb</u> on page 165

- <u>eval bottom up</u> on page 166

- find on page 169

- <u>get area</u> on page 176

- <u>get attribute</u> on page 178

- get build id on page 179

- get buswidth on page 180

- get cell area on page 181

- <u>get\_crosstalk\_threshold</u> on page 182

- <u>get\_crosstalk\_tolerance</u> on page 183

- get current instance on page 184

- <u>get\_current\_module</u> on page 185

- <u>get\_equivalent\_cells</u> on page 186

- <u>get global</u> on page 187

- get hdl file on page 188

- <u>get hdl hierarchy</u> on page 189

- get hdl top level on page 191

- <u>get hdl type</u> on page 192

- <u>get info</u> on page 193

- <u>get message count</u> on page 195

- <u>get\_message\_verbosity</u> on page 196

- get names on page 197

- <u>get net</u> on page 198

- <u>get\_parent\_instances</u> on page 200

- get state of design on page 201

- <u>get\_tempfilename</u> on page 203

- get version on page 204

- <u>help</u> on page 205

- <u>highlight</u> on page 206

- <u>issue message</u> on page 207

- limit on page 208

- <u>quit</u> on page 210

- read\_adb on page 211

- <u>read\_edif</u> on page 213

- <u>read\_symbol</u> on page 214

- <u>read\_symbol\_update</u> on page 215

- <u>read\_verilog</u> on page 216

- <u>read vhdl</u> on page 219

- <u>record\_macro</u> on page 222

- report area on page 223

- <u>report aware library</u> on page 226

- <u>report\_crosstalk\_violations</u> on page 227

- report design rule violations on page 229

- report fsm on page 231

- <u>report\_globals</u> on page 234

- <u>report hierarchy</u> on page 236

- <u>report path group options</u> on page 238

- <u>report\_resources</u> on page 240

- <u>report skewed clock pins</u> on page 245

- report vhdl library on page 246

- <u>report\_wire\_self\_heat\_violation</u> on page 247

- <u>reset crosstalk threshold</u> on page 249

- reset dont modify on page 250

- <u>reset\_failsafe</u> on page 252

- reset global on page 253

- <u>reset register type</u> on page 254

- <u>reset\_vhdl\_library</u> on page 255

- <u>reset wire self heat prevention</u> on page 256

- <u>set attribute</u> on page 257

- set\_aware\_component\_property on page 261

- <u>set aware library</u> on page 262

- <u>set cell property</u> on page 263

- <u>set current instance</u> on page 265

- <u>set current module</u> on page 266

- <u>set dont modify</u> on page 268

- <u>set\_dissolve\_hierarchy</u> on page 267

- set failsafe on page 271

- <u>set global</u> on page 272

- <u>set logic0</u> on page 273

- <u>set logic1</u> on page 274

- <u>set message count</u> on page 275

- <u>set message verbosity</u> on page 276

- <u>set path group options</u> on page 277

- <u>set port property</u> on page 279

- <u>set\_register\_type</u> on page 280

- <u>set table style</u> on page 282

- <u>set unconnected</u> on page 286

- <u>set\_vhdl\_library</u> on page 287

- <u>unalias</u> on page 289

- <u>write adb</u> on page 290

- <u>write\_edif</u> on page 292

- <u>write globals</u> on page 293

- <u>write verilog</u> on page 294

- <u>write\_vhdl</u> on page 296

#### ac\_shell

```

ac_shell [-64] [[-f] filename] [-cmdfile command_filename]

[-logfile log_filename] [-cdsdocd {on | off}] [-queue] [-expire] [-version]

[-help] [-continue] [-no_init] [-set var=value ...] [-which] [-gui]

[-display machine:0] [-geometry intxint+int+int] [-fullscreen] [-large]

[-limit] [-colormap_colormap_file] [-unique]

```

Starts the BuildGates Synthesis tool. For more detail on starting ac\_shell, refer to <u>Before</u> <u>You Begin</u> in the BuildGates Synthesis User Guide.

#### **Options and Arguments**

| -64                        |                                                                                                                                                                                                                                                                                                                                          |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | Starts a 64-bit ac_shell session instead of the default. <i>Default</i> : 32 bit                                                                                                                                                                                                                                                         |

| -cdsdocd {on   off}        | Enables or disables the use of browser-based documentation for ac_shell help. When set to on, the full documentation set is available from the <i>Help</i> button in the GUI. When set to off, only the syntax is displayed in the command line. <i>Default</i> : on when running in GUI mode and off when running in command line mode. |

| -cmdfile <i>command_fi</i> | <i>lename</i><br>Specifies the name of the command file.<br><i>Default</i> : ac_shell.cmd                                                                                                                                                                                                                                                |

| -colormap                  | Specifies the color map file.                                                                                                                                                                                                                                                                                                            |

| -continue                  | Does not exit after an error in Tcl script file.                                                                                                                                                                                                                                                                                         |

| -display machine:0         | Specifies the system display to use.                                                                                                                                                                                                                                                                                                     |

| -expire                    | Displays the expiration date of the license.                                                                                                                                                                                                                                                                                             |

| -f filename                | Displays name of Tcl script file to source at startup. You can use $filename$ without specifying the $-f$ .                                                                                                                                                                                                                              |

| -fullscreen              |                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | Allows using the entire screen for the ac_shell.                                                                                                                                                                                                                                                                                                                  |

| -geometry intxin         | <pre>ht+int+int Sets the initial size and position of the GUI main screen window. Where width and height are in pixels. And xoff and yoff are the number of pixels from the corner; a negative value is measured from the bottom or right corners, and a positive value is measured from the top or left corners. No spaces are allowed between the values.</pre> |

|                          | For example: -geometry 800x400+10-30 means create a window 800 by 400 pixels with its left edge offset 10 pixels from the left edge of the screen and its bottom edge offset 30 pixels from the bottom of the screen                                                                                                                                              |

|                          | Valid only in GUI mode.                                                                                                                                                                                                                                                                                                                                           |

| -gui                     | Invokes graphical user interface (GUI) mode                                                                                                                                                                                                                                                                                                                       |

| -help                    | Prints usage message for this command.                                                                                                                                                                                                                                                                                                                            |

| -large                   | Increases the memory limit above 2GB for the process running ac_shell if the memory is available.                                                                                                                                                                                                                                                                 |

| -limit                   | Prints the current datasize limit and memory allocation limit for the machine on which the software will run.                                                                                                                                                                                                                                                     |

| -logfile <i>log_fi</i> . | <i>lename</i><br>Displays the name of the log file.<br><i>Default</i> : ac_shell.log                                                                                                                                                                                                                                                                              |

| -no_init                 | Disables the sourcing of ~/.ambit/.acshrc                                                                                                                                                                                                                                                                                                                         |

| -queue                   | Waits for a license if none is available.                                                                                                                                                                                                                                                                                                                         |

| -set var=value | Initializes a Tcl variable.                                              |

|----------------|--------------------------------------------------------------------------|

| -unique        | Instructs the tool to create unique names for all command and log files. |

| -version       | Displays the version of this ac_shell.                                   |

| -which         | Displays the full path name of the ac_shell executable.                  |

#### Example

The following command starts the BuildGates Synthesis graphical user interface and saves the session log in  $cpu_design.log$ :

> ac\_shell -gui -logfile cpu\_design.log

#### **Related Information**

check option

#### add\_netconn

add\_netconn net\_id pin\_id\_list

Adds new net connections to the given net\_id in the current module. Place connections in the same module as the specified net.

This command does not delete the connection between the pin and the net if one already exists. It will create a generic buffer between the existing net and the new net.

To delete a net connection, use <u>delete netconn</u>.

Use caution when using the add\_netconn command. This command changes the connectivity of the netlist, which can change the functionality of the netlist. You may create timing loops, multiport nets, and short circuits, and connect multiple outputs to the same net. Use the <a href="https://www.change.check\_timing">check\_timing</a> and <a href="https://www.check.com">check\_timing</a> and <a href="https://www.check.com">and</a> and</a> and</a> and</a> and <a href="https://www.check.com">and</a> and</a> and</

#### **Options and Arguments**

| net_id      | Specifies the id of the net where you want to add connections. |

|-------------|----------------------------------------------------------------|

| pin_id_list | Specifies the id list of the pin you want to add to the net.   |

#### Example

The following command adds CLK pin connections of all the instances with the name out1\_reg\_\* to net1:

> add\_netconn [find -net net1] [find -pins out1\_reg\*/CLK]

#### **Related Information**

<u>create\_instance</u>

<u>create\_net</u>

<u>create port</u>

December 2003

## alias

alias command\_name name

Creates a simple alias for command names. It does not support aliasing a command with options to a new name. It only performs a simple renaming of a previously defined command.

A more general mechanism for renaming or repackaging commands is the built-in Tcl proc command.

### **Options and Arguments**

| command_name | Displays the alias name.                  |

|--------------|-------------------------------------------|

| name         | Displays the name of an existing command. |

### **Database Impact**

There is no effect on the database

## Example

This command creates the wv alias for the write\_verilog command:

> alias wv write\_verilog

### **Related Information**

<u>unalias</u>

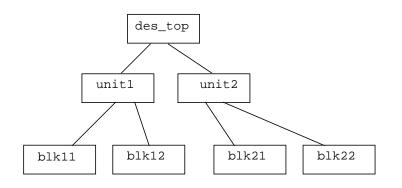

## all\_children

all\_children [-instances] [-hierarchical] [module\_id | module\_name]

Returns a Tcl list of object identifiers representing the child modules that are instantiated in the specified parent module. Use this routine recursively to traverse through the netlist in a top-down fashion, as shown in the example below.

**Note:** The list returned by the all\_children command excludes black box children unless you use the -instances option.

### **Options and Arguments**

| -instances                      |                                                                                                                                                                            |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 | Returns a Tcl list of object identifiers representing the instance_ids of the instantiated child modules in the specified parent module, including the black box children. |

| -hierarchical                   |                                                                                                                                                                            |

|                                 | Returns the module_ids (or the instance_ids if the -instances option is specified) of all the modules instantiated in the specified module and its submodules.             |

| <pre>module_id   module_n</pre> | ame                                                                                                                                                                        |

|                                 | Specifies the object identifier or name associated with a module.<br>If neither is specified, the command returns the children of the<br>current module.                   |

### Examples

The following command gets the names of children of module a:

```

> get_names [all_children [find -module a]]

b c

```

■ The following command writes a netlist for all children of module a:

```

foreach i [all_children [find -module a]] {

set_current_module $i

write_ver $i.ver

}

```

The following command traverses the hierarchy using attributes:

```

proc traverse_hier {mod} {

set_current_module $mod

```

```

foreach i [all_children] {

traverse_hier $i

}

if {[get_attribute [find -module $mod] MY_ATTR] == ""} {

set_attribute [find -module $mod] MY_ATTR "visited"

# do action

}

```

## **Related Information**

<u>all parents</u>

<u>find</u>

## all\_parents

all\_parents [module\_id | module\_name]

Returns a Tcl list of object identifiers of modules that instantiate the specified module, similar to the all\_children command. This routine is used to do a bottom-up traversal of the netlist hierarchy.

## **Options and Arguments**

module\_id | module\_name

Specifies the object identifier or name associated with a module. If neither is specified, the command returns the parents of the current module.

## **Related Information**

<u>all\_children</u>

<u>find</u>

## bg\_shell

```

bg_shell [-64] [[-f] filename] [-cmdfile command_filename]

[-logfile log_filename] [-cdsdocd {on | off}] [-queue] [-expire] [-version]

[-help] [-continue] [-no_init] [-set var=value ...] [-which] [-gui]

[-display machine:0] [-geometry intxint+int+int] [-fullscreen] [-large]

[-limit] [-colormap_colormap_file]

```

Starts the BuildGates Synthesis tool. For more detail on starting bg\_shell, refer to <u>Before</u> <u>You Begin</u> in the *BuildGates Synthesis User Guide*.

### **Options and Arguments**

| -64                        |                                                                                                                                                                                                                                                                                                                                          |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | Starts a 64-bit ac_shell session instead of the default. <i>Default</i> : 32 bit                                                                                                                                                                                                                                                         |

| -cdsdocd {on   off}        | Enables or disables the use of browser-based documentation for bg_shell help. When set to on, the full documentation set is available from the <i>Help</i> button in the GUI. When set to off, only the syntax is displayed in the command line. <i>Default</i> : on when running in GUI mode and off when running in command line mode. |

| -cmdfile <i>command_fi</i> | <i>lename</i><br>Specifies the name of the command file.<br><i>Default</i> : bg_shell.cmd                                                                                                                                                                                                                                                |

| -colormap                  | Specifies the color map file.                                                                                                                                                                                                                                                                                                            |

| -continue                  | Does not exit after an error in Tcl script file.                                                                                                                                                                                                                                                                                         |

| -display machine:0         | Specifies the system display to use.                                                                                                                                                                                                                                                                                                     |

| -expire                    | Displays the expiration date of the license.                                                                                                                                                                                                                                                                                             |

| -f filename                | Displays the name of the Tcl script file to source at startup. You can use <i>filename</i> without specifying the -f.                                                                                                                                                                                                                    |

|                            |                                                                                                                                                                                                                                                                                                                                          |

| -fullscreen              |                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | Allows using the entire screen for the bg_shell.                                                                                                                                                                                                                                                                                                                 |

| -geometry intxint        | <pre>s+int+int Sets the initial size and position of the GUI main screen window. Where width and height are in pixels. And xoff and yoff are the number of pixels from the corner; a negative value is measured from the bottom or right corners, and a positive value is measured from the top or left corners. No spaces are allowed between the values.</pre> |

|                          | For example: -geometry 800x400+10-30 means create a window 800 by 400 pixels with its left edge offset 10 pixels from the left edge of the screen and its bottom edge offset 30 pixels from the bottom of the screen                                                                                                                                             |

|                          | Valid only in GUI mode.                                                                                                                                                                                                                                                                                                                                          |

| -gui                     | Invokes the graphical user interface (GUI) mode.                                                                                                                                                                                                                                                                                                                 |

| -help                    | Prints the usage message for this command.                                                                                                                                                                                                                                                                                                                       |

| -large                   | Increases the memory limit above 2GB for the process running bg_shell if the memory is available.                                                                                                                                                                                                                                                                |

| -limit                   | Prints the current datasize limit and memory allocation limit for the machine on which the software will run.                                                                                                                                                                                                                                                    |

| -logfile <i>log_file</i> | Displays the name of the log file.<br>Default: bg_shell.log                                                                                                                                                                                                                                                                                                      |

| -no_init                 | Disables the sourcing of ~/.ambit/.acshrc                                                                                                                                                                                                                                                                                                                        |

| -queue                   | Waits for a license if none is available.                                                                                                                                                                                                                                                                                                                        |

| -set var=value | Initializes a Tcl variable.                             |

|----------------|---------------------------------------------------------|

| -version       | Displays the version of this bg_shell.                  |

| -which         | Displays the full path name of the bg_shell executable. |

## Example

The following command starts the BuildGates Synthesis graphical user interface and saves the session log in cpu\_design.log:

> bg\_shell -gui -logfile cpu\_design.log

### **Related Information**

<u>check\_option</u>

# bgx\_shell

```

bgx_shell [-64] [[-f] filename] [-cmdfile command_filename]

[-logfile log_filename] [-cdsdocd {on | off}] [-queue] [-expire] [-version]

[-help] [-continue] [-no_init] [-set var=value ...] [-which] [-gui]

[-display machine:0] [-geometry intxint+int+int] [-fullscreen] [-large]

[-limit] [-colormap colormap_file]

```

Starts the BuildGates Extreme Synthesis tool. For more detail on starting bgx\_shell, refer to Before You Begin in the BuildGates Synthesis User Guide.

### **Options and Arguments**

| -64                        |                                                                                                                                                                                                                                                                                                                                           |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | Starts a 64-bit bgx_shell session instead of the default. <i>Default</i> : 32 bit                                                                                                                                                                                                                                                         |

| -cdsdocd {on   off}        | Enables or disables the use of browser-based documentation for bgx_shell help. When set to on, the full documentation set is available from the <i>Help</i> button in the GUI. When set to off, only the syntax is displayed in the command line. <i>Default</i> : on when running in GUI mode and off when running in command line mode. |

| -cmdfile <i>command_fi</i> | <i>lename</i><br>Specifies the name of the command file.<br><i>Default</i> : bgx_shell.cmd                                                                                                                                                                                                                                                |

| -colormap                  | Specifies the color map file.                                                                                                                                                                                                                                                                                                             |

| -continue                  | Does not exit after an error in Tcl script file.                                                                                                                                                                                                                                                                                          |

| -display machine:0         | Specifies the system display to use.                                                                                                                                                                                                                                                                                                      |